采用Virtex-5嵌入式三模以太网MAC进行设计

|

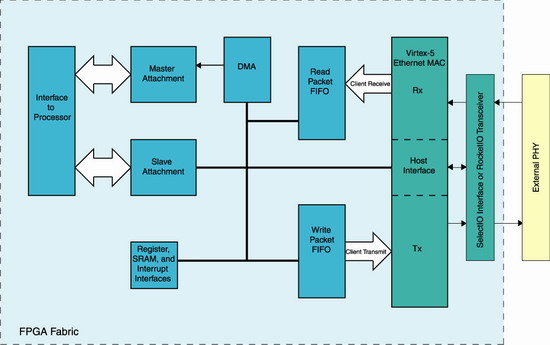

| 图2:在Virtex-5 FPGA上,MAC连接到一个处理器 |

工具和IP支持

Xilinx通过CORE Generator软件、LogiCORE™ IP和参考设计对以太网 MAC提供支持。

Virtex-5 以太网 MAC 封装

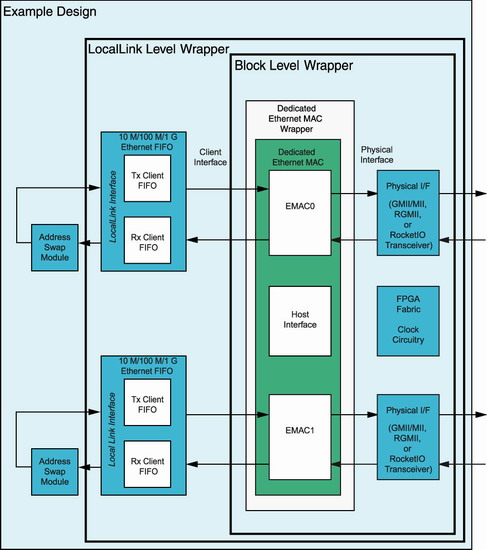

图3显示了一个HDL封装的模块结构图,它可以从Xilinx的 CORE Generator工具中获得。

图3:Virtex-5以太网MAC封装的模块结构图 以太网 MAC是一个具有162个端口和79个参数的复杂组件。封装文件使您可以仅对特定应用所需端口的参数和接口轻松进行设置。它们的另外一个优势是简化了时钟和物理I/O资源的使用。 作者: Nick McKay Xilinx公司高级设计工程师 |

Xilinx公司 FPGA Mac MDIO DCR RGMII PHY 相关文章:

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)