如何采用FPGA协处理器实现算法加速

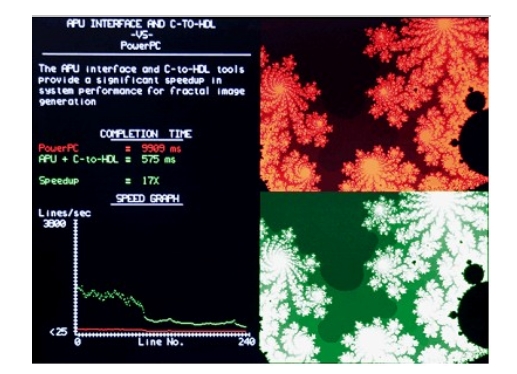

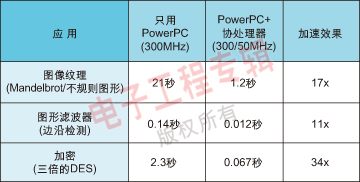

图4:Mandelbrot图 表2:通过协处理器加速器的算法加速性能对比 作者:Glenn Steiner,高级工程经理,glenn.steiner@xilinx.com

本文使用CoDeveloper工具组作为C-HDL工具组用于该设计实例,而且只修改了软件Mandelbrot C程序以使其与C-HDL工具兼容。其中的改变包括:将软件项目分割成不同的进程(顺序执行的独立单元);函数接口转换(硬件到软件)到流;增加编译器指令来对产生的硬件进行优化。我们随后使用CoDeveloper工具组来创建Pcore协处理器,将该协处理器输入到Xilinx Platform Studio(XPS)。利用XPS,我们将PC连接到PowerPC APU控制器接口,并测试系统。

Xilinx公司的应用说明资料XAPP901中提供了该设计的全面描述和设计文件,并提供下载。同时,用户指南UG096提供一种实现设计实例的逐步设计指导。

我们对Mandelbrot图像纹理问题、图像滤波应用和三倍DES加密的性能改善进行了测量。性能改善显示了从11倍到34倍的加速,在表2中做出了总结。

受功率、尺寸和成本的约束,你可能需要做出一个并非理想的处理器选择,通常所选择处理器性能比期望的性能低。当软件代码不能运行足够快时,协处理器代码加速器成为一种很有吸引力的解决方案。你可以在HDL中手动设计加速器或使用C-HDL工具自动将C代码转换成HDL。

使用Impulse C这样的C-HDL工具能使加速器运行更快且更简单。Virtex-4 FX FPGA具有两个嵌入式PowerPC,能实现处理器指令流水线到软件加速器之间紧密的连接。如上所述,关键的软件程序增加速度10倍到30倍,使300MHz的PowerPC提供等于或高于高性能GHz级处理器的性能。上面的实例每个只需要几天的时间来产生,显示了采用C-HDL流程的快速设计、实现和测试。

Kunal Shenoy,设计工程师,kunal.shenoy@xilinx.com

Dan Isaacs,嵌入式处理总监,dan.isaacs@xilinx.com 赛灵思公司先进产品分部

David Pellerin,首席技术官,david.pellerin@impulsec.com Impulse Accelerated技术公司

FPGA DMA CPU APU FIFO FCB HDL 相关文章:

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)