设计性能:物理综合与优化

时间:04-28

来源:赛灵思公司

点击:

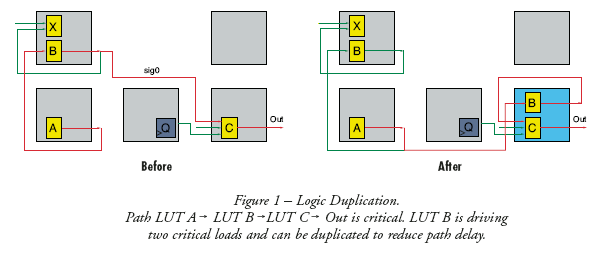

工艺技术的发展极大地提高了 FPGA |0">置位置离驱动源的距离太远因而无法满足时序要求时,可以复制该 LUT 或触发器并放置在靠近该组负载的地方,从而减小布线延迟(图 1)。

逻辑重组:如果关键路径跨越多个切片中的多个 LUT,可利用较少的切片对该逻辑进行重新组织,采用时序上更高效的 LUT 与多路转换器组合来降低该路径所需的布线资源(图 2)。

逻辑重组:如果关键路径跨越多个切片中的多个 LUT,可利用较少的切片对该逻辑进行重新组织,采用时序上更高效的 LUT 与多路转换器组合来降低该路径所需的布线资源(图 2)。  |

|

|

结论

赛灵思工具集中的物理综合与优化功能将进一步走向成熟并随着每个软件版本的发布进行扩展。伴随效果质量的改进,您可以期待着对优化类型的更多控制。其他计划中的强化措施还包括在再优化阶段考虑更多设计单元(例如允许将寄存器移入和移出 I/O 块或块 RAM 和 DSP 块等专门功能),以及将布线阶段包含进物理综合迭代过程,以及优化系统。

赛灵思 ISE 软件中的物理综合与优化工具是为在实现的打包和布局阶段对您的 FPGA 设计的结构进行重新检查而创建的。给定时序约束和物理版图信息,在映射和布局布线阶段优化综合决策可极大地改进结果。

作者:赛灵思公司 Kevin Bixler ISE 技术营销经理;David Dye 高级技术营销工程师

赛灵思 DSP EDA FPGA ASIC RAM ISE UCF 相关文章:

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 赛灵思与微软汽车业务部推出的智能车载信息系统(06-18)

- 实现多端口1Gbps 和10Gbps TCP/iSCSI 协议处理任务卸载解决方案(07-10)

- 嵌入式串行 ATA 存储系统(07-27)

- 基于SRIO协议的板级芯片互联技术(01-13)

- 插值查找表:实现DSP功能的简便方法(04-08)