DDR SDRAM在嵌入式系统中的应用

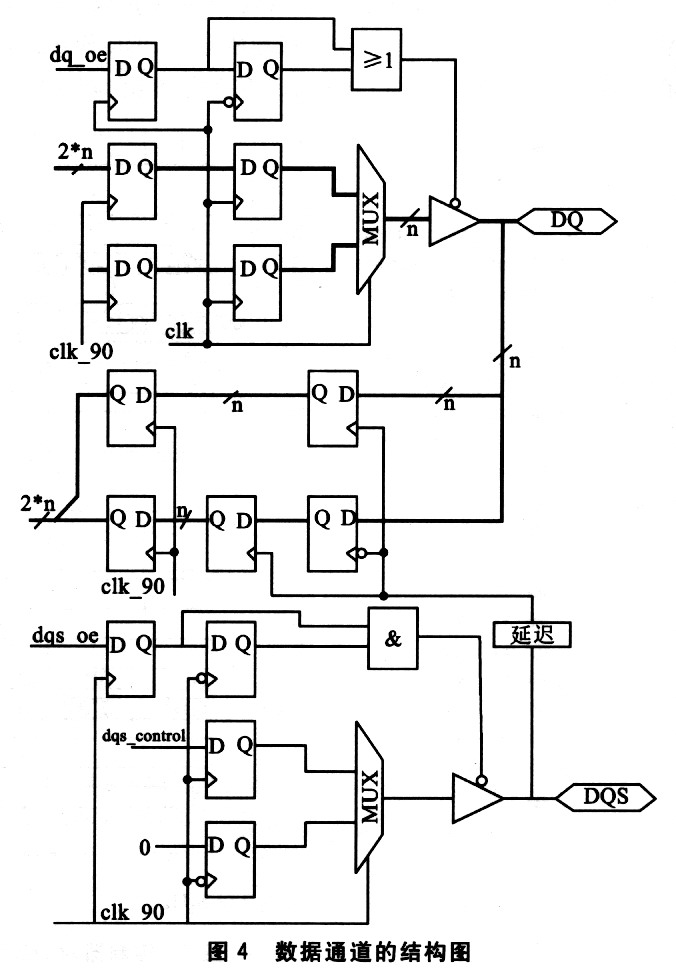

图4中完整地显示了控制器读和写数据通道上DQ与DQS的结构关系。前面提到过,Cyclone系列FPGA没有带DDR触发器的输入输出单元,但完全可以用靠近输入输出引脚处的逻辑资源来实现DDR触发器,而且最后的结果表明,这种实现方式可以满足时序要求。

从图4中也可以看到,控制器内部有两个时钟,clk和clk_90,两者之间的相位差为90°。图中将面向存储器的时钟命名为clk。它是clk_90时钟的90°相位延迟后的信号。clk_90作为系统时钟来驱动整个FPGA,clk时钟驱动存储器接口电路。

3.2.1 DQS相位延迟电路

在读周期中,DDR SDRAM输出的DQ和DQS信号是边沿对齐的。为了使用DQS作为选通信号来捕获DQ,DQS信号需要在FPGA内部相对于DQ信号作90°的相位延迟。但是这个延迟不能使用锁相环(PLL)来完成,因为DQS信号不具有时钟的特性。因此,需要在DQS和读数据时钟之间加一个延迟链(delay chain),如图4中所示。

前面提到过,Cyclone系列FPGA在其DQS输入引脚上有一个专用的延迟单元,用来使DQS相对于DQ信号产生一个90°的相移。因此,可以使用该硬核资源来完成对DQS的相移,而不必通过内部的逻辑来搭建这样一个延迟电路。从而可以获得更好的时序性能。

3.2.2再同步

读周期中,从DDR SDRAM来的数据信号首先通过延迟后的DQS锁存到DDR触发器中。为了在FPGA内部能够使用该数据,还要将其同步到FPGA内部的时钟域上,这个过程称为再同步(resynchronization)。如图4所示,对于前一级DQS延迟后的信号锁存的数据再通过clk-90同步之后才送到内部数据总线上。

在写周期中,DQS与DQ必须是中心对齐的(centerahgn)。我们用clk_90时钟触发的DDR触发器产生DQS信号,因此,为了满足时序要求,从内部来的数据通过clk_90时钟锁存后再由clk触发的DDR触发器将其输出,从而保证DQs与DQ是中心对齐的。

4 控制器的实现

该控制器针对16位宽512 Mb的DDR SDRAM设计,在Altera公司的Quartus II4.2环境中采用Cyclone系列的EPlC6Q2410C6来实现,总共使用了729个逻辑单元,占FPGA可编程逻辑资源的12%,此外还使用了1个锁相环(PLL)。最后,在Modelsim 5.8中对整个工程进行布局一布线后仿真(Post-P1ace&RouteSimulation),采用的模型为Micron公司的512 Mb的DDR SDRAMMT46V32M16的仿真模型,时钟为133 MHz,图2是控制器读取DDR SDRAM的时序仿真波形。

5 结 论

本文给出了一种通过FPGA控制将DDR SDRAM应用在嵌入式系统中的方法。设计中采用Altera公司性价比较高的Cyclone系列FPGA,并充分利用片内提供的锁相环、DDR触发器以及DQS延迟链等硬件资源,占用的逻辑资源少。该设计可以很容易地移植到Altera公司其他系列的FPGA上,经过适当的修改还可以用来控制64位宽的DIMM型的DDR SDRAM,因此可以很好地应用在需求高速度、大容量存储器的场合中。

- 利用 Xilinx FPGA 和存储器接口生成器简化存储器接口(07-27)

- 以高达666 Mbps 的速率在Spartan-3E FPGA 中实现 1:7 的解串行化(08-03)

- 利用 Virtex-4 器件实现 QDR II SRAM 接口(08-03)

- 使用 Virtex-4 器件实现的 DDR2 的控制器(08-03)

- 提高存储器子系统效率的三种方法(04-07)

- IR推出高效解决方案为DDR3内存模块提供动力(09-21)