安森美:PLL技术将进一步取代传统晶振时钟方案

时间:10-13

来源:与非网 周方

点击:

"硅基锁相环(PLL|0">PLL)时钟解决方案将继续替代传统晶振(XO)技术以满足更高频率、复杂度及系统同步对时钟解决方案的要求,"安森美半导体标准产品部全球市场营销副总裁麦满权在近日的新型时钟解决方案发布会上对记者说。随着系统设计复杂度的日益增长,原有的时钟解决方案已经不能满足用户在复杂环境下的设计需要,特别是在具有多个分离元器件的系统当中。

作为高速数字电路设计过程中最为关键的技术之一, 系统时钟设计的好坏, 直接影响到整个系统的最终性能。市场研究机构Databeans调查表明,2007年全球时钟市场收入为16亿美元,预计2007年至2012年总时钟市场年复合增长率(CAGR)将达到11%。然而,在这个市场中,传统晶振解决方案由于容易受到温度、电压、负载等外界因素的影响,已经很难满足用户的设计需求,麦满权解释说。而自动化测试设备、计算机、网络通信及消费类电子产品不断提升的设计复杂度及数据传输速率却越来越强烈的需要用户寻找一种能够整合更多频率时钟器、支持多种I/O接口的时钟技术,并且同时实现更低的抖动(低于1 ps)、更高的电磁干扰(EMI)抑制要求等系统性能。

传统晶振技术的应用

作为传统时钟解决方案,晶振顾名思义就是晶体振荡器。它能够提供非常高的初始精度并且具备较低的温度系数,被广泛应用于彩电、计算机、遥控器等各类振荡电路以及用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号的通信系统中。

但是由于晶振是利用石英晶体压电效应制成的一种谐振器件,很容易受到外界环境条件和电路元件选择的影响,电路元件的选择和线路板布局的不同都对其性能造成影响。此外,电磁干扰(EMI)、机械震动与冲击、湿度和温度这些因素都会因为增大输出频率的变化,从而增加系统的不稳定性,并且在有些情况下,造成电路停止运作。

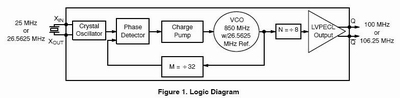

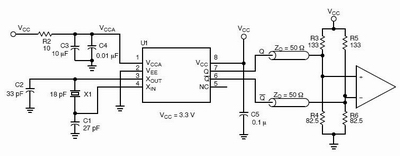

晶振符号与晶振产品样图 PLL技术的优势PLL技术主要是用来统一整合时脉讯号,分配内存资源工作,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。 在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。因此,所有板卡上各自 80MHz和20MHz时基的相位都是同步的,采样时钟也是同步的,从而实现系统在同一时刻下严格数据采集的功能。

|

- Atsushi Abe加入安森美半导体董事会(03-03)

- 安森美完成收购赛普拉斯CMOS图像传感器业务部(03-03)

- 现代汽车照明及安森美半导体先进汽车照明解决方案(03-17)

- 安森美半导体瞄准中国汽车制造业(03-13)

- 安森美推出高精度NCP590系列双输出CMOS低压降稳压器(09-11)

- 安森美发布超低电容ESD保护器件ESD9L(09-18)