PADS在原理图中调换了IO口后再同步到PCB如何才能不删除该管脚上的布线?已找到方法

时间:10-02

整理:3721RD

点击:

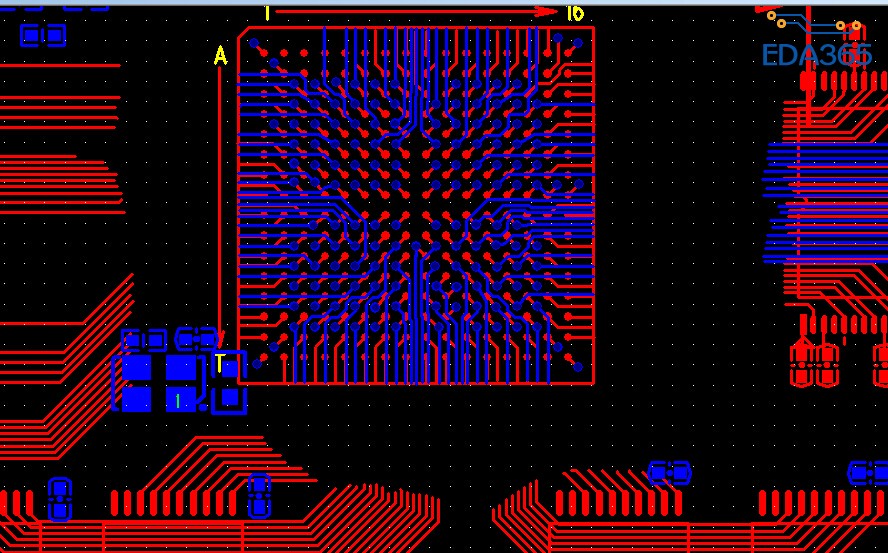

各位老师好:现在在画一块FPGA的板子,有大量IO需要调整,我先从原理图里面调试IO管脚,然后同步到PCB中,但是每次一同步过去PCB中的变动的过管脚的走线就会被删除掉,这种情况要怎么样才能不被删除呢?如下图所示:扇出好的BGA同步在原理图中换了一下管脚后所有相关的布线全没了,真是伤脑筋啊,求解脱的方法。

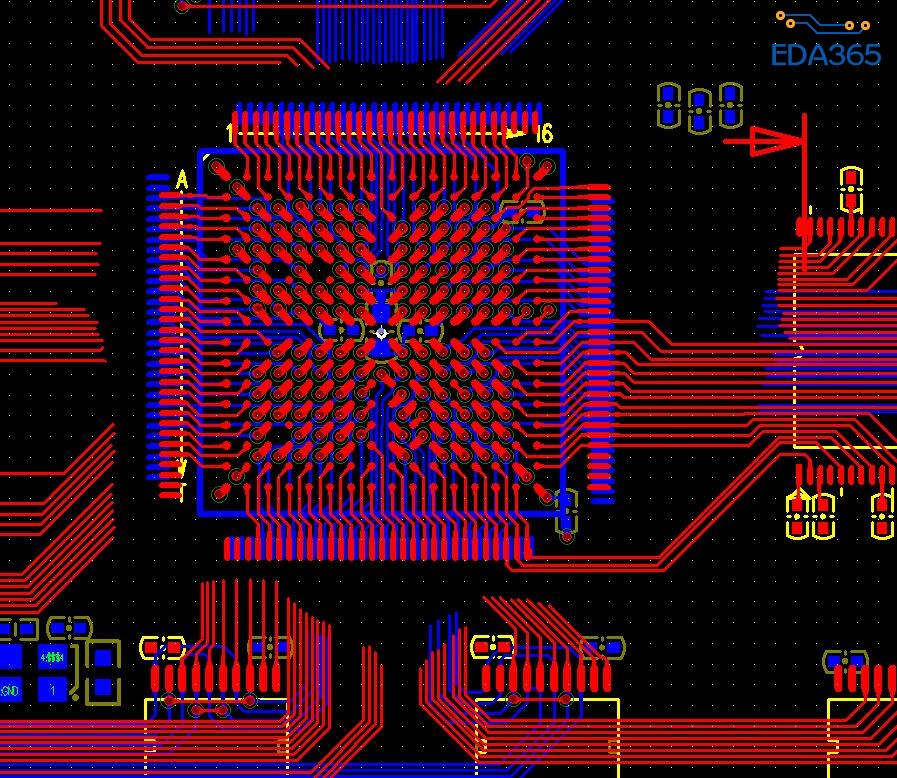

经过几天的煎熬,终于找到一个自认为比较好的方法,供大家参考。如下图所示,我先反BGA所有IO全部扇出,然后用做一个封装将所有的IO与之相连,并且生成新的网络名,然后再把这部分电路放到文件中去与最方便的网络相连,相连的时候选择用原电路中的网络名,网络对接完成后删除用来连接的元件,最后从PCB反向同步到原理图,就算完事了。

经过几天的煎熬,终于找到一个自认为比较好的方法,供大家参考。如下图所示,我先反BGA所有IO全部扇出,然后用做一个封装将所有的IO与之相连,并且生成新的网络名,然后再把这部分电路放到文件中去与最方便的网络相连,相连的时候选择用原电路中的网络名,网络对接完成后删除用来连接的元件,最后从PCB反向同步到原理图,就算完事了。

貌似很难办到,有一种方法你可以试下看看行不行,把PCB fan-out好的线reuse保存好,导完PCB后,在reuse进来

PADS这个软件最不好的地方就是这个,同步就飞线,resue实现不了

真是伤脑筋啊,求解脱的方法。

谢谢,我尝试了一下,这样也不太理想,这样做再导入进来复用的线路但是还在,但是复用的线路网络属于建立复用时候的网络名,这样一来即使把复用的线贴到BGA上去,网络也不不对的,并且没有办法单独修改复用模块上的网络名,一改就连同PCB中的网络一起改了。我也尝试过新建立一个PCB导入这个复用模块,但是软件他会认为文件中不含有这些网络的其它对象,因此不能导入这个复用。

我是复用一份放着,然后同步过来,在用复用的那部分直接COPY

你好,在ECO模式下把PCB的PIN间网络互换,也就是说在板子上进行IO网络调整,这种情况下走线不掉,再导入原理图就一点问题也没有了。

这个问题有谁研究出更好的方法么!求分享

看看~學習一下~

这样只适合少量的管脚对调吧?多了难免会乱...而且,能达到小编要求的那个效果?

熟能生巧。效果可以达到。有兴趣的可以试下。

你这个是确实是可以,但是只能少量的时候用,像我这个几百个脚全盘重新定义的话不太方便