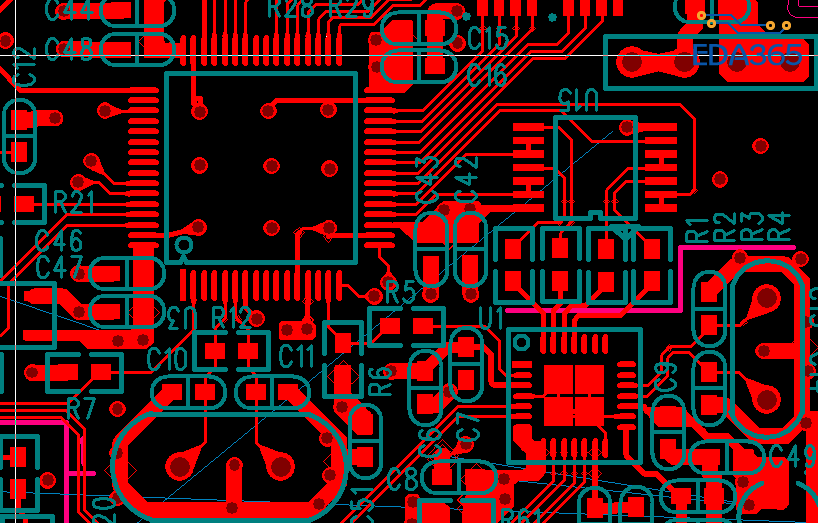

关于线路板打EFT出现问题麻烦看看

主芯片用的STM32F0系列的,有个ADE7953的采样芯片。

电源部分X,Y电容,共模电感都有了的。然后主板是四层板,而且该处理的基本都注意到了。

但是打EFT测试的时候,会卡死一样(也不是死机)只要人手挨到线路板半厘米左右 ,又可以正常工作了,然后就是无限循环的卡,挨,卡,挨。

有人分析说是布板的问题,但是我真觉得能注意的都注意了,没办法了。

后来我把ADE7953和主芯片的连接断开,不管怎么打,都不会死机了。

现在很郁闷 不知道该怎么办了,而且为什么会手挨近就会启动,怀疑静电,但是什么三防漆和静电纸都用过了还是一样的情况。

有没有有经验的人士分析下。

你的板子,看起來非完整版本.

gnd 沒處理好.(你還是不看pdf第68頁.)

c7一支腳未下gnd.(要接不接c6腳的地.)

代表你檢查不完整.

pdf第68頁

所有ADE7953 電源電容(共6個)的地(不打via)要先接pin14和pin16再接至中間大pad(你的是4片pad).

这些都不是问题,因为最后我也覆铜了的。不要说PDF第68页,连DEMO板我都看了很多次了。

問題是ADE7953 電源電容(共6個)的地(不打via)要先接pin14和pin16再接至中間大pad(你的是4片pad).....是不能覆铜了的,要分開只能靠ic 中間腳下地.

LAYOUT GUIDELINES

Figure 78 presents a basic schematic of the ADE7953 together with its surrounding circuitry, decoupling capacitors at pins VDD, VINTA, VINTD, and REF, and the 3.58 MHz crystal and its load capacitors. The rest of the pins are dependent on the particular application and are not shown here. Figure 77 presents a proposed layout of a printed circuit board (PCB) with two layers that have the components placed only on the top of the board. Following these layout guidelines will help in creating a low noise design with higher immunity to EMC influences. The VDD, VINTA, VINTD, and REF pins each have two decoupling capacitors, one of μF order and a ceramic one of 220 nF or 100 nF. These ceramic capacitors need to be placed closest to the ADE7953 as they decouple high frequency noises, while the μF ones need to be place in close proximity. The exposed pad of the ADE7953 is soldered to an equivalent pad on the PCB. The AGND, DGND, and PULL_LOW pins traces of the ADE7953 are then routed directly in to the PCB pad. The bottom layer is composed mainly of a ground plane surrounding as much as possible the through hole crystal pins.

佈局指南

圖78給出了ADE7953的基本原理圖連同其周圍的電路,在引腳去耦電容VDD,VINTA,VINTD和REF,以及3.58 MHz晶振和負載電容。銷的其餘都依賴於特定的應用,這裡不再顯示。圖77提出了一個印刷電路板(PCB)的兩層具有只放在板的頂部的部件的建議設計。遵循這些佈局指南將有助於創造一個低噪音設計,具有更高的免疫力EMC的影響。在VDD,VINTA,VINTD和REF引腳各有兩個去耦電容,一個μF和220 nF的陶瓷一個或100 nF。這些陶瓷電容器需放置最接近的ADE7953,因為他們去耦高頻噪聲,同時μF的必須到位近在咫尺。該ADE7953的露出焊盤焊接到PCB上的等效墊。該AGND,DGND和PULL_LOW引腳ADE7953的痕跡,然後被直接發送到PCB焊盤。底部層主要由周圍盡可能貫通孔晶體引腳接地平面。

pdf 它的意思是只靠中間pad下地, 而去耦電容VDD,VINTA,VINTD和REF 共8個,你都打了via,又可能覆铜.

要把去耦電容VDD,VINTA,VINTD和REF 共8個,就近拉ic pin4,14,16不打via(地要隔開), 只靠中間pad下地.

不好意思没能完全体会你的话,首先你说那8个电容连到一起再连到中间的PAD我能理解, pin4,14,16不打via(地要隔開),地要隔开这里是什么意思?VINTA,VINTD这两个脚我引出来还有用,如果光靠中间的PAD引出到那么细的管脚再引出到我后面用的部分不是更不保险。而且我是四层板为了保持地的完整性,如果不就近VIA的话,外围一圈地,就只有信号线打VIA了。

是原廠要求pin4,14,16 只能在靠中pad下地, 所以連接到去耦電容的地直接拉到pin4,14,16 ,千萬不要在去耦電容端下地的via,

而在pin4,14,16拉至去耦電容也要和其他地"隔開",接至中間pad再用via下地.

是不讓其他外界的地,直接影響ic的兩種地,靠ic中間的地來整合ic兩種地的乾淨,不受外界影響,所以pin4,14,16拉至去耦電容的地對外要"隔開".

你用过这个芯片没有以前?看你说的好像很熟悉。

也许你说的很有道理我试试看吧。

但是这个东西不好说,唉,以前我问过ADI的工程师,说要各种地隔开,而且不能接在中间PAD,我保证这是ADI工程师给我的原话,具体可以看ADE7953的中文版。

后来我确定不用磁珠或者0电阻隔开效果更好,但是与主芯片通讯信号会影响,又是代理的告诉我让画四层板,或者说让我们全盘隔离。

代理?不一定專業,因為大家都是出來"混"一口飯.

英文好不代表能代理電子零件.

因為他們有些很少在量產廠打滾,而我打滾過.