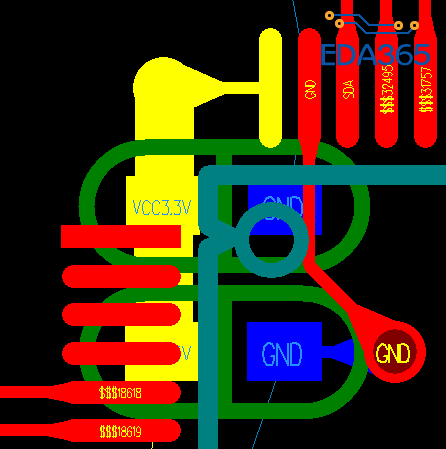

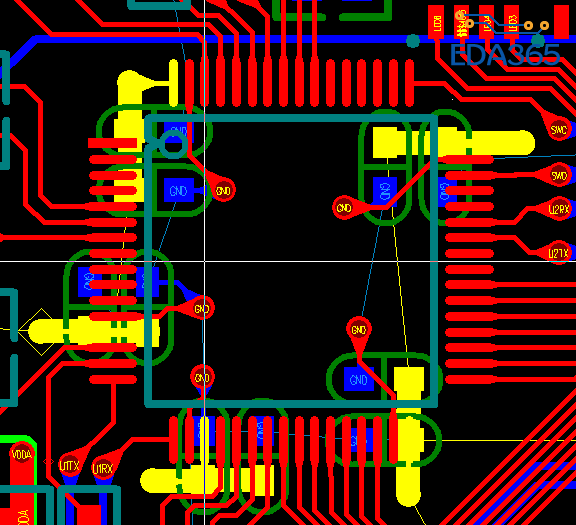

如图所示滤波电容。

时间:10-02

整理:3721RD

点击:

一般芯片推荐滤波电容都是1UF1NF级别的并在芯片电源端口,如我画的这个图,四层板,电源端口在芯片边缘,芯片在顶层,滤波电容在地层,最后芯片中间肯定我要画一大块地的,请问像我这样可以么?还有这种情况最好的处理办法是什么?我也看过JIMMY的书,但是那种电容滤波都是最理想的情况下。很多板基本都不能达到多打孔。

还有就是假如电容命名为1,2,然后1,2是并联的,我是把1的电源端打一个过孔到电源层,然后在2的电源端打一个到电源层,然后还是1连到2然后在过孔练到芯片?

还有就是假如电容命名为1,2,然后1,2是并联的,我是把1的电源端打一个过孔到电源层,然后在2的电源端打一个到电源层,然后还是1连到2然后在过孔练到芯片?

还有个问题四层板,3层为POWER ,晶振下面的POWER那里不需要隔离出来吧,就是一整个电源层。

不需要

不用

1 从芯片出来的电源线与封装的焊盘同宽,尽量短的打孔到第三层。然后从孔走20mil以上的线宽(BOTTOM层)尽量短到滤波电容。

2 晶体下面的不需要隔离。

3 你的泪滴太丑了。把那个CURVED点上。

谢谢

不用