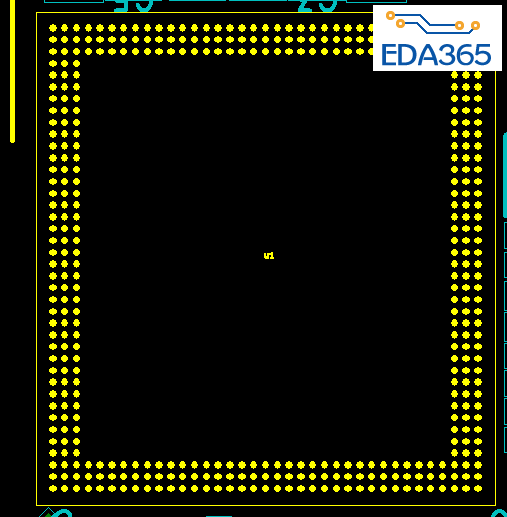

单颗DDR3 6层板的画法

时间:10-02

整理:3721RD

点击:

如上图所示,准备用6层(不是用4层),有T点等长,目前想法是:L1走线,L2 GND (少量线),L3全GND , L4走线 , L5 VDD电源 L6全GND;

不知这样是否合理,请大家评论,谢谢。

这是pop的ddr,中心间距应该是0.4mm,如果是6层1阶的板,ddr的线尽量走在第1层(少量ddr线),第2层(主要ddr线),第3层为参考地。

如果是6层2阶的板,ddr的线尽量走在第1层(少量ddr线),第2层(少量ddr线),第3层(主要ddr线),第4层为参考地

DDR3 一般用的都是通孔

还是多参考芯片手册,就这张图看不出来

POP的DDR这样搞有点蛋疼吧

6层2阶不可能太贵了,这个是平板一DDR3离CPU近1.5mm,我觉的第三层(主GND)走CPU到DDR3的所有线,但DQS CLK放在第四层并包GND ,L5为VDD,这应该是合理的走法。

不知道你的平板是啥方案的,如果用6层1阶的话,你想把ddr的线主要走在第3层,要看主芯片那是否有空间打那么多盲孔和埋孔,

另外,ddr3的跑频比较高,对DQS CLK的要求就比较严格,尽量要做到立体包地。

至于电源呢,不可能分配1层来走电源,主要是没那么多空间

MTK,如按你的做法,L2主DDR线,L3是主GND, 那么L4是T点两边PIN的走线,L5为VDD,你说的DQS CLK立体包GND还是做不到。

DQS CLK走在第4层,第5层的电源平面,也可以作为DQS CLK参考平面

对,这样才比较合理。