溺死在Jimmy培训的菜鸟——《电源完整性设计》培训心得

时间:10-02

整理:3721RD

点击:

原本的偶,在浴缸里扑腾几下,没被淹死,就以为自己会游泳了~

这次参加Jimmy的培训,一个一个的巨浪打过来,才明白什么叫知识的海洋……

这次主讲是92年的肖美女~

自卑啊~人家美女这么年轻,就已经如此有气场了~

而且讲得也非常有条理、深刻……

比较有感觉的就是,不墨守陈规,敢于突破教条,懂得灵活变化……

这也在于“知其所以然”!如果只是知其然,必不敢,也不懂得去灵活的变通。

只有知其然亦知其所以然,才懂得、敢于去变,去优化~

OK,废话说得有点多了~

下面,偶就跟大家分享一下,偶这次培训的笔记~

纯属抛砖引玉~

一、何谓电源完整性设计

电源完整性设计研究的是电源分配网络PND(既从电源的源头-稳压芯片-平面-芯片引脚到芯片内部这么一个网络)。

二、电源完整性的目标

电源完整性设计就是要把噪声控制在允许范围内,保持芯片焊盘上的电压稳定。

如何做到这点呢?这就要求我们知其所以然了——噪声从哪来?通过控制哪些量能控制噪声呢?

电源的波动,其实是由芯片内部造成的!

芯片内部状态转换过程,电流必定会产生变化,而这个变换就导致了纹波的产生。

这个电流的变化是不可避免的!那么根据欧姆定律我们要让波动保持在一定范围内,就只有让阻抗尽量低!

三、电源完整性的实现方法

1、电源模块

电源模块一般靠近板边、电源入口摆放。

但也不要教条地就认死这一规则。如果某电源模块,只是给单独一芯片而不是整板供电,自然就放在芯片附近即可。

2、内层平面

尽量使电源层有紧耦合的参考地平面。这其实本身就相当是一个电容,比外接的电容要强大的多~

叠层时一般都是对称的,并保证至少有一个电源与地紧挨着。

两个压差较大的电源平面不允许在一起。

3、多种电源的分割

分割后的电源平面要尽量规则。这不是为了美观,而是为了避免出现瓶颈。

不要将没有联系的平面之间形成交叠,空间上也不允许重叠。

即分割后的相同平面(如模拟或者数字)无论在哪一层的投影都应该是形状相同,位置相同的。

1Oz铜厚时1mm的线宽能通过的电流分别为:表层1A,内层0.5A。

VIA则按孔的周长来等效走线宽。如0.25mm的孔,周长为0.25*3.14=0.785mm,可通过的电流为0.785A.

4、供电芯片

大电容谐振频率低,滤波半径较大,可放在芯片周围;

小电容谐振频率高,滤波半径较小,必须靠近芯片引脚摆放。

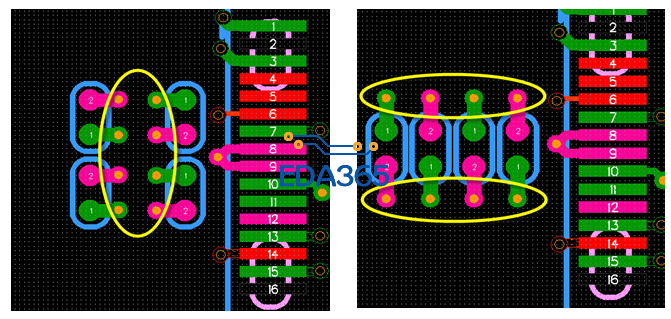

为了降低电容的等效电感,可以采用多个相同容值电容并联的方式进行滤波。并且摆放是要正反交错,以让电感相互抵消。

上面我就回顾、总结一下,偶这菜鸟在这知识巨浪里头,偶尔挣扎着吸取到的一些东西。

不够完整,甚至可能会有些理解上的偏差,还望各位多多指教~

下面我想用本次培训的几道思考题作为结尾:

1、为什么大电容可以放在距离芯片较远的位置,小电容要尽量靠近芯片管脚放置?

2、如何估算线宽和过孔的过流能力?

3、叠层是否是走线层越多越好,只要保证电源能连通就可以?

4、为了降低电容的等效电感,可以采用多个相同容值电容并联的方式进行滤波?

狂顶!

写的不错

顶一个

寫得不錯,學習喲

不错,赞一个

辛苦

LZ,92年的肖美女也在论坛里哦,试着将她挖出来嘛,年轻貌美又有实力,多好啊~~~

你认为偶发这篇文章是干嘛的呢?

还不就是为了吸引肖美女过来~

有美女一定要頂,也學習了

谢谢分享!

顶楼上的想法!

我们老板临时要我们周末两天都加班,产品要赶出来去参展。然后清明放四天假。

相当悲催的我

显然你被你们老板忽悠了——本来清明就有三天假,你加了两天班,应该有五天假~

学习了,谢谢分享!