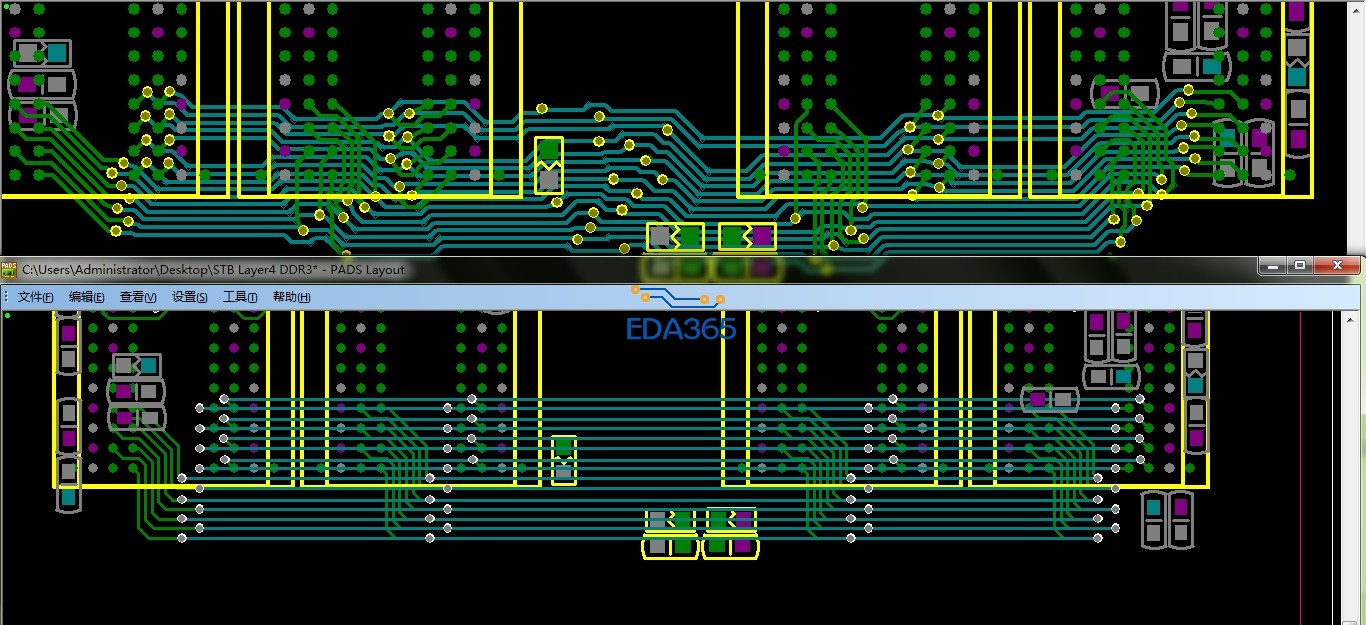

新手DDR3走线,请大师点评一下此两种走线有什么差别?

坚持自己,等你出错的那一天。你就会做的和别人一样了。嘎嘎。

说说原因呗.

你直直的走线,还有电源和地没有扇出,这些VIA 要打哪里?除去空间有影响,其本是没有什么影响的

相信直线的更好,因为我也是走直线,说说原因

1.在打via的时候明显第一种会将电源和地平面打断,影响信号回流(建议你的可以吧你的via的距离拉大一点让铺铜时能铺过去).

2.扇出好一个DDR的地址线后可以直接copy到其他DDR上面减少工作量(如4楼说的你应该吧电源孔和地孔扇出)

3.走成直线很有规律方便做等长(从左到右DDR编号为1234,用上面copy的方法可以直接让:12间地址线的长度=34间地址线的长度)

4.做T点时,T点会很整齐,只需要找好两个t点,其他t点都能够按照栅格对齐即可,方便快捷

5.貌似你的第一幅图是不满足3W原则,而整齐的走直线可以很容易满足3W.

当然也有不好的地方就是这样会让地址线无形中变长。

上面是个人的看法,有什么不对的地方请各位高手指点

DDR3芯片的速率是800M到1.6G,速度最低也的800M,这时候信号完整性问题就来了!

1.按您的布线,直线部分没有stub,但外面的线stub太长

2.您走线的拓扑是T点,还是菊花链?不管是那种现在的走线都有信号完整性问题,系统工作将不稳定。

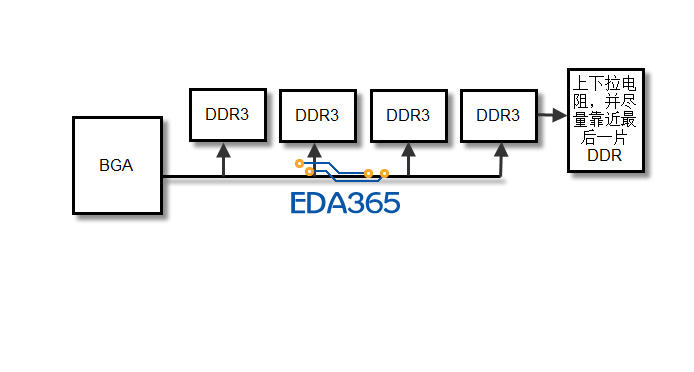

DDR3-四片的最好拓扑结构是菊花链,DDR3扇出尽量不出芯片,上下拉电阻靠近最后一片DDR,分段等长,以DQS为基准,误差25mil,以确保信号完整!菊花链如图所示:

我怎么记得地址线要和CLK 线长度比拟才好呢?误差不超过200mil?请确认!

其实你给的两种我觉得都不好! 首先左边7跟跟右边的几根拓扑结构都不一样!这样不好吧!

能做到最好为什么不做呢?如果空间实在是不够,误差可以大一点。FYI,我是给Jimmy老大打下手的,以上内容都是听Jimmy讲课的知识总结。

stub太长了点.......

6楼正解 还有 过孔不要打在一起了 除了好看点没得其他用处 但是你把参考平面全破坏了!

高手如云啊

高手~~大大的多

高手如云啊

学习了,请继续讨论