DDR等长规则的相关问题,请Jimmy大师帮忙

时间:10-02

整理:3721RD

点击:

1.对于一般一带二的DDR2/DDR3的数据线分组是否分为四组,分别为D[0_7]、D[8_15]、D[16_23]、D[24_31]?

数据组同一组的容差为多大?不同组的容差为多大?

2.两片SDRAM分别各有一个时钟信号,L_CK/L_CKN和M_CK/M_CKN,同组差分对容差为多大?两片SDRAM的时钟信号线长度容差为多大?

3.四组数据信号的DQS[0-3]长度根据时钟信号线长度,容差为多大?

4.地址、控制、时钟分为一组,组内容差为多大?

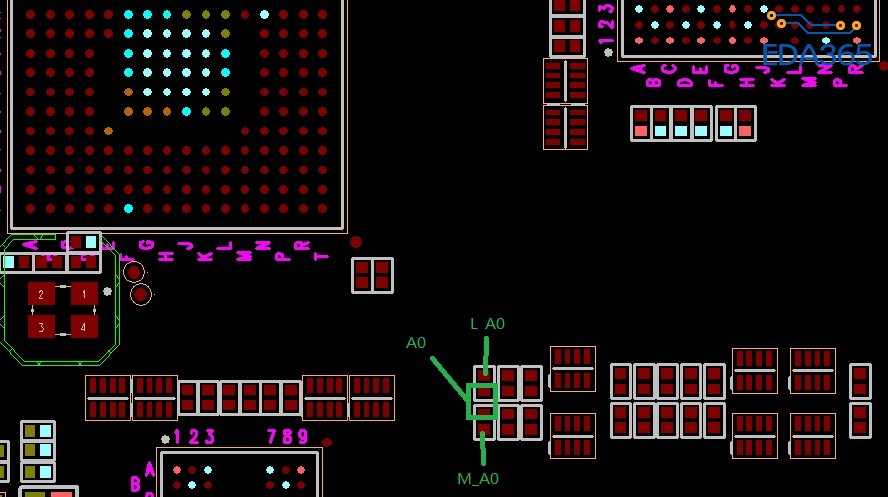

5.如图所示,如果两片SDRAM的地址、控制、时钟信号分别有各自的串阻和排阻,且如图中布局,是否相当于形成了虚拟T点?

在进行等长设置时,地址线是否应该分为两段进行长度匹配(电阻前和电阻后),两段的容差分别为多大?

数据组同一组的容差为多大?不同组的容差为多大?

2.两片SDRAM分别各有一个时钟信号,L_CK/L_CKN和M_CK/M_CKN,同组差分对容差为多大?两片SDRAM的时钟信号线长度容差为多大?

3.四组数据信号的DQS[0-3]长度根据时钟信号线长度,容差为多大?

4.地址、控制、时钟分为一组,组内容差为多大?

5.如图所示,如果两片SDRAM的地址、控制、时钟信号分别有各自的串阻和排阻,且如图中布局,是否相当于形成了虚拟T点?

在进行等长设置时,地址线是否应该分为两段进行长度匹配(电阻前和电阻后),两段的容差分别为多大?

这个问题事实上坛子里有很多人给了说明,JIMMY大师也说了很多次,估计也没几个人愿意重复说。

友情提示:多看看书了在在坛子里问。

这里我给你说明,所有的容差范围都围绕你产品的工作频率来设定范围的,频率高则范围小,频率低则范围大,都是相对的,需要根据芯片的规格进行计算。

但是在设计的时候一般我们可以做的严格一些,尽量防止我们的产品出现超出范围的情况。

而一般 我们的时钟差分内控制是在5MIL内,数据组是组内10MIL 地址控制命令和时钟一起是50MIL 这是高频率的一般做法不代表绝对正确。

回答你的问题

1:DDR的数据为8位一组,加上差分DQS和DM一共11根, 组内10MIL等长, 组和组之间不用等长。

2 时钟差分组内5MIL等长,2片之间10MIL等长。

3 这个分2种 DDR3不用等长 DDR2根据芯片资料计算等长范围。

4地址控制命令和时钟一组等长一般都可以做到50MIL。

5绝对不是,这个请仔细查看虚拟T点的介绍。

排阻和电阻不用前后两端都等长 只需要一起等长就行

非常感谢!