PCB阻抗设计问题

下图为一个四层板叠层TOP-GND-VCC-BOT的两张截图,现在有几个问题不大清楚,请各位高手指教,谢谢!

1.需要进行阻抗匹配的网络,是尽量不要使用过孔转层还是一定不能使用过孔转层走线呢?

2.如果使用了过孔走线转层,又有什么要求呢?

3.使用了过孔转层后,如图所示,其网络阻抗会有两个值(不管转了几次,在多少层上走过),有些这两个值相同,有些不同,这是为什么呢?

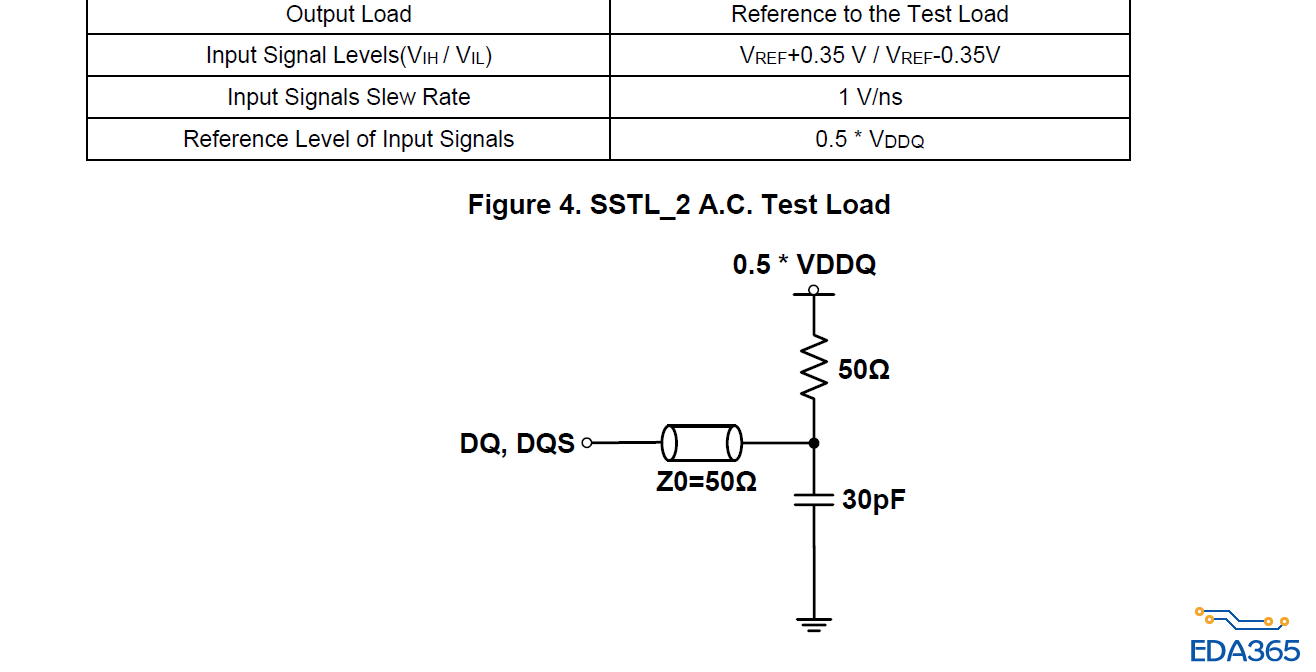

4.到底哪些线需要进行匹配阻抗,阻抗值取多少?这个是在规格书上有要求(如图三某款SD RAM规格书截图)还是一些特性的信号线的要求呢?

1:

理论上,走线上过孔越多对信号质量影响越大,但是实际中不能满足,所以在频率G级别以下的走线是可以打孔的,不过不能太多,

至于你说的阻抗要求,你打板时可以向板厂指明要求,板厂会帮你调整的,如果你自己想计算,请参考SI9000这一款软件

2:

换了层的话,参考层就会跟着变的,比如你的TOP层参考GND,而走到BOT的话,参考层就会变成VCC,

3:

PCB上那个数据参考值不准确,按板厂实际生产来参考,

影响阻抗的条件是, 板厚,板材的介电常数,走线的宽度,还有就是铜皮的厚度,如果不同的话,可能是板子的厚度变了,(就是TOP 到GND 的距离 和 VCC 到BOT的距离不一样,)所以会不一样,

4:

常用的阻抗要求走线有:

天线---50

USB走线----90

HDMI走线--------100

DDR 单端数据线和地址线-----50

差分线的话是100

还有一些特殊的要看SPEC上有要求没,

以上个人观点,如不当请指正!

非常感谢您的解释。接触这一块不久,所以很多东西都是模棱两可。

一、关于其中第二点,是否可以这样理解:1.我上面实验图片的四层板顶层和底层走线厚度相同,内层两层的铜皮厚度也是相同,上下两层到相应参考层的距离也是一样; 2.在第一幅图中,我在中间加了一个过孔,过孔的前段线走的是顶层,后段线走的是底层,因为线宽一样,所以其阻抗值应该也是一样,就是PADS上的显示值相同(如果此处忽略过孔造成的阻抗不连续因素的话,可以认为此网络为阻抗连续的?); 3.在第二幅图中,我加了三个过孔,四段线分别走的是顶层/地层/电源层/底层,因为顶层和底层阻抗一致(和图一中的一样为55),而两个内层的阻抗因为线宽和厚度相同也是一致为65(此时电源层走线网络的参考层就是地层而地层走线网络的参考层应该就是电源层了吧?),所以在第二幅图中会显示两个阻抗值?那么也就是代表此网络的阻抗是不连续的?如果我改变它在内层的走线宽度来减小阻抗而使其与表层走线一致,是否也大致可认为整个网络阻抗走线没变化了呢,至少会比原来显示55-65的效果要好些吧?

二、再就是关于带有特性阻抗要求以及等长要求的PCB设计步骤的问题,一般是否就是按照以下步骤来进行呢:

1.查看规格书以及按照一般的经验(例如您在上面第4点中提的),罗列出那些有特性阻抗要求以及等长要求的网络;

2.根据项目和系统要求,确定PCB的叠层结构(有点搞不懂,是不是只有当网络的相邻层有像GND和VCC这样的参考层时特性阻抗才存在或者叫才有意义?换句话说,我一个普通的双面板,两面都是走的线,然后灌了铜,那么它上面随意的一个网络走线是否也可以做特性阻抗呢?)

3.根据您在上面第1点的回复中提到的Polar SI9000,结合确定好的叠层结构,计算走线所需要的宽度;

4.在PADS中按照Polar计算出的数据进行布线,布好后此网络属性中显示的阻抗值理论上应该是接近第3步中在Polar中设定的值吧(也就是第1点中确认的阻抗值)?而关于有等长要求的网络组,则在ROUTER中设置好其等长属性,然后通过蛇形线之类的方式使其在设置的长度、误差范围内实现走线?

5.完成PCB后导出Gerber资料,并注明所有有阻抗要求和等长要求的网络信息给板厂,让他们进行处理。

写的有些多,只是尽量想说清楚

谢谢!

这一整套做下来会比较累,比较省力的方法是把要求给厂商,让他们给你叠构数据。毕竟你的理论值到厂里做的时候还是要根据实际来补偿的,知道阻抗可以怎么调整,心里有个大概的数就,别被厂商忽悠了就OK了。

谢谢!

实际操作确实这样就可以了,省心省事。就像您提到的,别让板厂忽悠就行了,现在也是想多多了解些。那上面我描述的那个步骤有问题么?

步骤这样可以了,也要看产品,如果是一般的设计,直接让厂商给参数就行了。要是对阻抗要求比较高的,我建议看完规格书就找厂商讨论叠构设计,尤其是材料以及PP和CORE的厚度。确定完以后,再走线。