四层板一个DDR ,不好等长怎么办?

时间:10-02

整理:3721RD

点击:

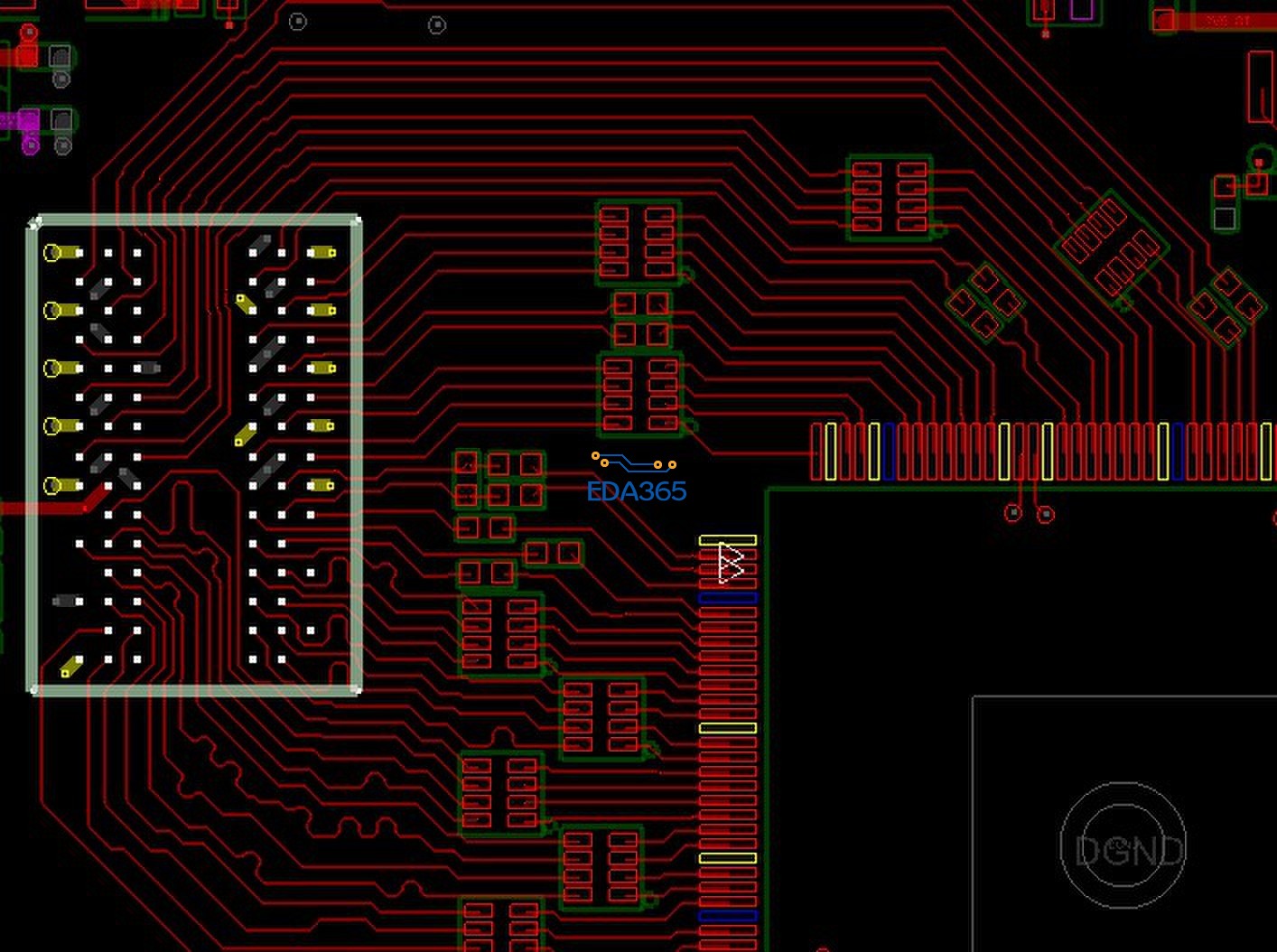

线宽5MIL 线距12MIL 数据等长25MIL 地址等长100MIL 所有的线都走在TOP层。难道我的DDR非要45度才行吗?

有谁走过类似情况的,发个图啊。我参考下啊。

有谁走过类似情况的,发个图啊。我参考下啊。

DDR

JIMMY在哪里。

调整下memory的方向吧,蛇形线可能要多些了。实在不行,真的要45度了。 另外, 线的间距12个Mil可以调整下吗?给等长腾出点空间。

芯片下面不是还有那么多位置啊

在下愚见,你这样走不太好,DDR中间的走线间距会很小

线距完全没必要12,走5没问题的,目测这个ddr只会跑800的

数据在哪里,地址在哪里?

呵呵。昨晚群里问你了。上半部分是数据,下半部分是地址。我现在我改为TOP面走数据。BOT面走地址了。

可以尝试一下把DDR往上面靠主芯片那里挪一点,感觉上面的线比较长而下面的短些,挪一点到时候等长都差不多长了如果在误差范围内要再绕等长就不会太辛苦。

一组数据走top层,另外一组走bot层,解决

也不怎么好搞。地址线。TOP与BOT都走线了。这样没问题吧?

跟地址线有什么关系。地址线不一直在top层吗?

没有。数据全走TOP层了。一部分地址也走TOP层。BOT层也走了一部分地址线。

在你的第一个图中,将其中十根数据线走在BOTTOM层就解决 了

不是优先保证数据线同层吗?