很急,求助:LVDS的走线

时间:10-02

整理:3721RD

点击:

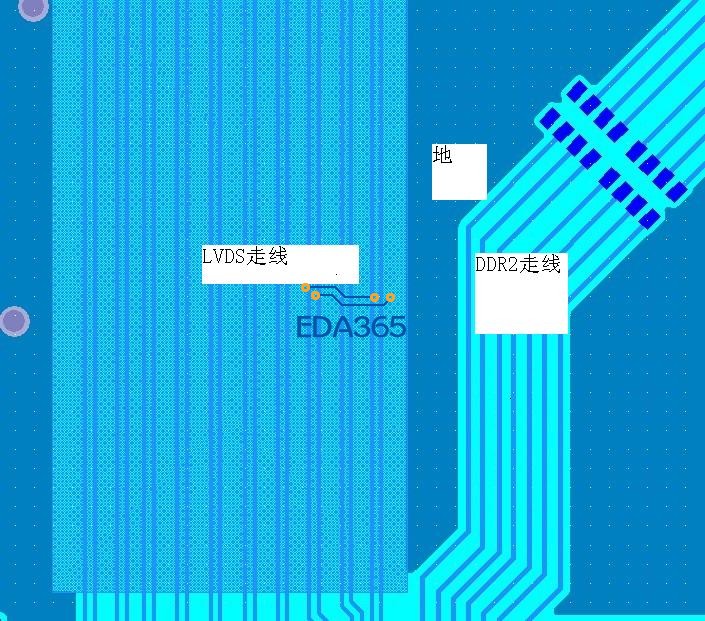

我板子里面有LVDS和DDR2走线离得比较近,我DDR走线向右挪动了一下,这样LVDS线和DDR线之间有一块地铺进来了。但是不能打地孔,因为下层有走线,请问这样的话能保证DDR和LVDS都能正常工作吗?

期待答案,学习。

怎么没人回答呢?自己顶一下

这要看你的DDR和LVDS走线所对应的平面层是否是完整的地平面,在两者之间的铜皮地最好有地孔,是为了减少信号的返回路径,减少干扰,还有LVDS线间应该也要有包地,LVDS都市差分走线,每对差分线之间都要包地,严格点,阻抗要达到100欧姆+/-10%的误差,此处的差分走线必须等长为先

没问题的,但是要注意LVDS的时钟线和数据走线保证4W以上,LVDS的时钟线和DDR走线不能靠太近,至少5W以上

如果没有打孔,建议删除中间的地铜,避免天线效应

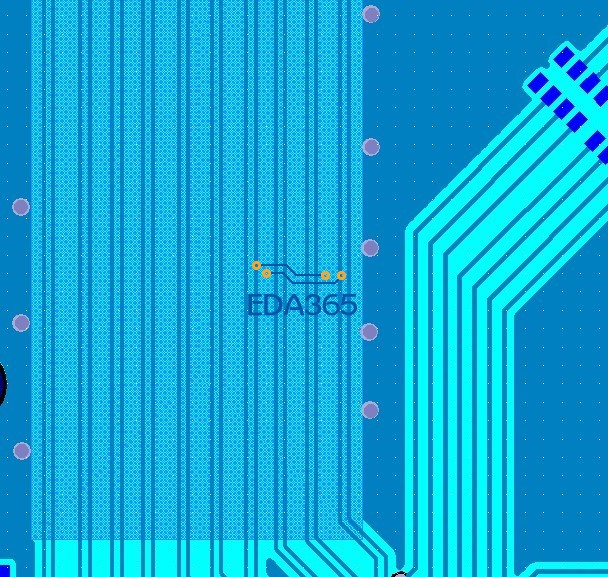

我把线调整了一下,LVDS走线做了禁铺,禁铺两边有包地,如何?

最好在LVDS的 CLK Pairs上增加包地,比全包有效,还要保证养分对的阻抗!

评论的很给力

那这个禁铺还用画吗?

建议删除中间孤立的地铜,或者想办法在DDR与LVDS之间的地铜加一些过孔。至少加两到三个,一端加在插座处,一端加在CPU处,中间再想办法加一个。

如果没办法加。那就删除中间孤立的地铜。完全可以跑起来,请放心使用。

谢谢!

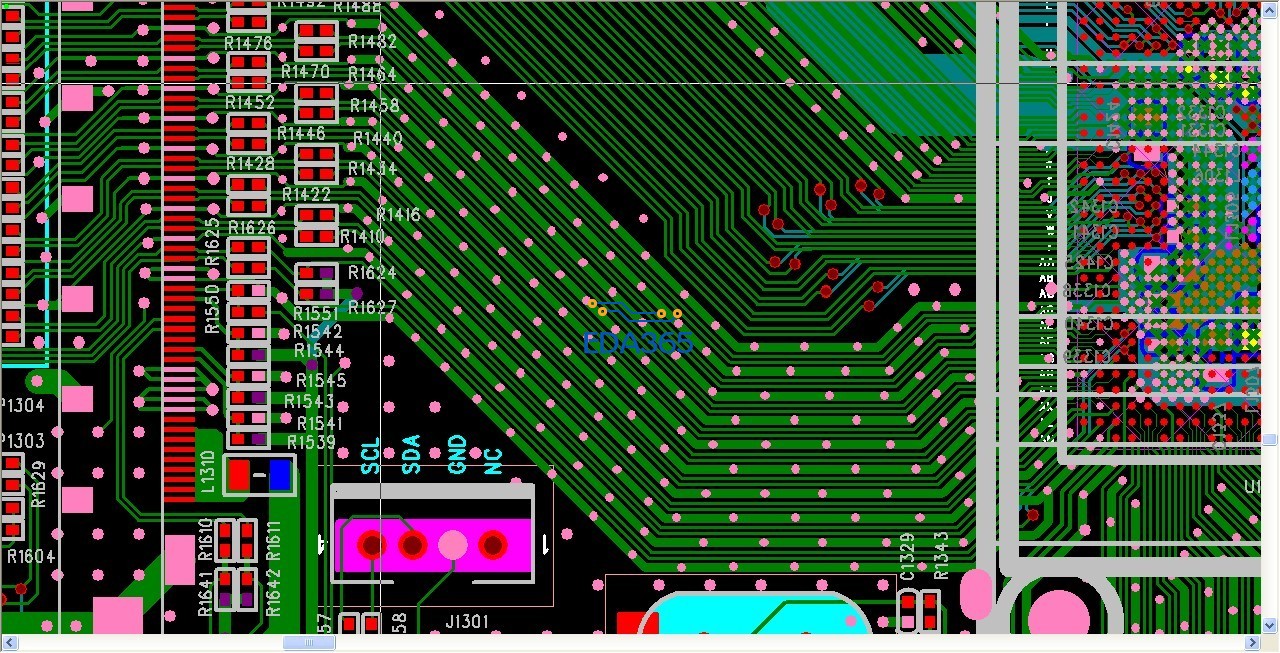

如果你这个板是双面板,在有空间的情况每个差分对用20~24mil走线包地,并且在地线上打过孔效果肯定最好的,可以保证由于底面地平面分割造成的EMI。如果是四层或六层有参考地,那可以按小编的方式,用Keepout把差分对内的Copperpour禁布。

两层板LVDS线GND包地打孔

请问差分对用20~24mil走线包地和只打地孔不连底线有什么区别吗?

如果只包地,不打孔,阻抗会不连续吧,我们一般都边地打孔。