有源晶振底下可以布线吗,布线长度是不是越短越好呢?

时间:10-02

整理:3721RD

点击:

有源晶振底下可以布线吗,布线长度是不是越短越好呢?

晶振地下不可以走线,布线尽量短,直,不饶弯。

是不是整个振荡电路部分底下都不能走线

还是仅仅晶振下方不能走线

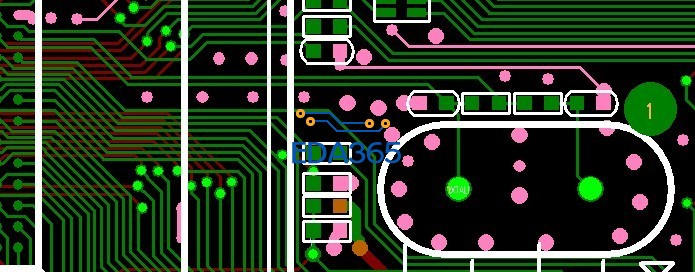

我的做法是:最基本的保证晶振屏蔽罩下方不走线,并多打地孔,防止干扰,尽可能使晶振的两个引脚引出的线都都包地打孔。如图所示

你这个好是好,但是也有个不好的地方,晶振离芯片好像蛮远。

如果有地平面隔着,下方可以走线。

时钟,复位线不可以。

没办法,有一个屏蔽罩放在那里,近不了

看看

来看看

请问大虾:晶振底下可以全部铺铜吗?这样会不会对晶振输出有影响?

这个晶振线走得也太长了点吧,这个跟EE工程师的要求有关吧, 我们以前公司都是底部全部挖空处理的!

挖空无非就是把TRACE的对地电容减小一部分,对于频率的影响并不明显(PCB对地的电容相当于增加了两个负载电容的容量)。而且就算是有影响,也可以通过调节那两个负载电容来纠正。

同意,虽然大家说得都不完整,但是都看了就有个完整的印象了