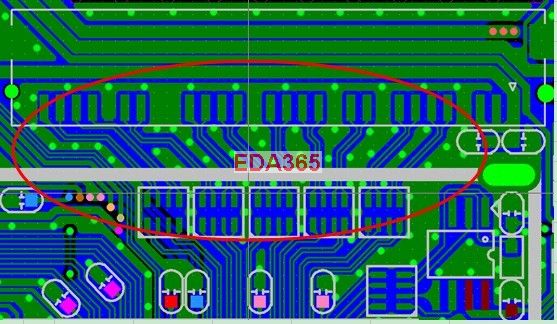

LVDS部分走线

时间:10-02

整理:3721RD

点击:

PCB说明:

1VDS的供电电路尽量靠近其端子的供电引脚,而且供电线宽>=40MIL.

2VDS的走线应以差分对的形式走线.并且要走在同一层面.有空间时每组差分对间能包地处理,尽可能多打过孔.与外界之间尽量用打有过孔的地线来隔离.如上图示.

3VDS座子尽量不要放置太远,LVDS走线不宜太长,避免和AFT,RF_AGC,I2C等到tuner的线靠近并排走

4:串在信号线中的排阻或者排感尽量靠近MST主芯片放置.对EMI有好处.

5:按照板层数决定线宽,线间距,经验值如下:

两层板:板厚1.6mm,介电常数4.5,1盎司铜厚,100欧姆差分线:线宽=12mil,线间距=6mil;90欧姆差分线:线宽=16mil,线间距=6mil.

四层板:板厚1.6mm,介电常数4.5,1盎司铜厚,100欧姆差分线:线宽=6mil, 线间距=6mil;90欧姆差分线:线宽=8mil, 线间距=6mil.

1VDS的供电电路尽量靠近其端子的供电引脚,而且供电线宽>=40MIL.

2VDS的走线应以差分对的形式走线.并且要走在同一层面.有空间时每组差分对间能包地处理,尽可能多打过孔.与外界之间尽量用打有过孔的地线来隔离.如上图示.

3VDS座子尽量不要放置太远,LVDS走线不宜太长,避免和AFT,RF_AGC,I2C等到tuner的线靠近并排走

4:串在信号线中的排阻或者排感尽量靠近MST主芯片放置.对EMI有好处.

5:按照板层数决定线宽,线间距,经验值如下:

两层板:板厚1.6mm,介电常数4.5,1盎司铜厚,100欧姆差分线:线宽=12mil,线间距=6mil;90欧姆差分线:线宽=16mil,线间距=6mil.

四层板:板厚1.6mm,介电常数4.5,1盎司铜厚,100欧姆差分线:线宽=6mil, 线间距=6mil;90欧姆差分线:线宽=8mil, 线间距=6mil.

共享一下啊

顶一下,小编也是做TV的吗,PCB画的很漂亮,不知道阁下做这个产品多久了

功力深厚啊!

看看。

确实画得不错,应该做了多年了吧?

太高手了

貌似双面板不好做阻抗啊