请教:四层板去耦电容走线问题?

时间:10-02

整理:3721RD

点击:

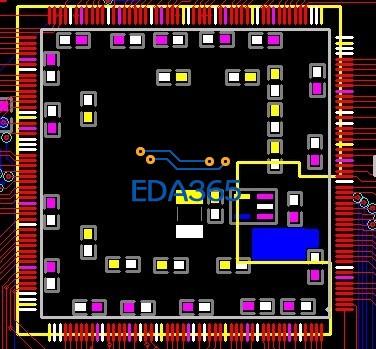

请教,四层板,内电层分别是一个GND层,一个VCC层。请问,去耦电容如果放置在背面,主要IC放置在顶层的情况下,去耦电容如何走线?

如上图所示,黄色的为3.3V,紫色为1.2V,白色为GND。主芯片在顶层,QFP封装,去耦电容在背面。四层分别是顶层,GND层,VCC层(包含3.3和1.2)底层。请问去耦电容该怎么走线才能符合电源(VCC和GND)先进入电容,再流入芯片的电源引脚(VCC脚和GND脚)。

那个是平面分割的问题 不是摆件的问题 再说了 平面分割的话你的孔位置也很重要 在VCC层直接加平面就行了 没有什么先和后 其实所谓的电源平面就是个铺铜 GND孔直接会被接入到TOP L2GND BOTTOM的GND铺铜面上 看来老兄需要补习下PCB培训内容啊

哈哈,你就说该怎么走线,怎么打孔就是了,说的条理点,看不明白你说的啥。

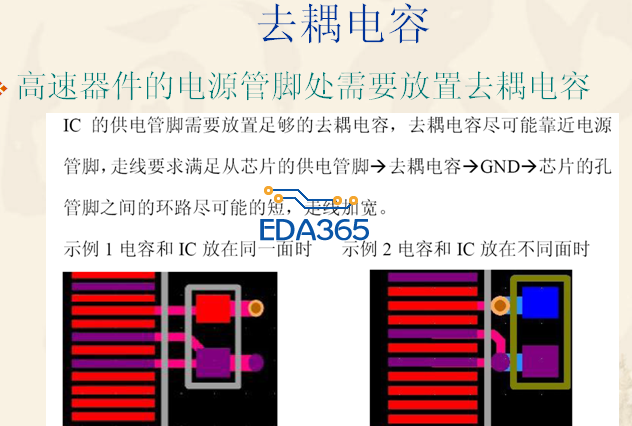

去耦电容要靠近PIN脚,对于我们这个去耦电容的放置,有个类似的放置我们可以参考一下,如贴图。

图二:

对不起呵,大十字鼠标放在图上了,以后我会注意一下~

所发图中,去耦电容放置在背面,VCC流向为:

VCC电源层——过孔——芯片VCC管脚,去耦电容的VCC端被短路掉了。

GND的流向:GND层——过孔——芯片的GND管脚,感觉去耦电容的GND段也被短路掉了?会不会出现上述的情况呢,还是多虑了啊?

jimmy小编 图中的连接方案就是最优的了。空间充足的情况下就按小编的方法最好了,满足电源层------滤波电容----IC的电源管脚的顺序了。

去耦在同面的情况好理解,去耦在背面的情况呢?

就近单点接地 这个是入行级的问题了