BGA F484的1.0间距电容怎么放置,怎么叠层更合理?

时间:10-02

整理:3721RD

点击:

第一次用BGA封装!

准备用六层通孔板,叠层就是S1、G1、S2、P、G2、S3。

主要就是不知道电容怎么放置?

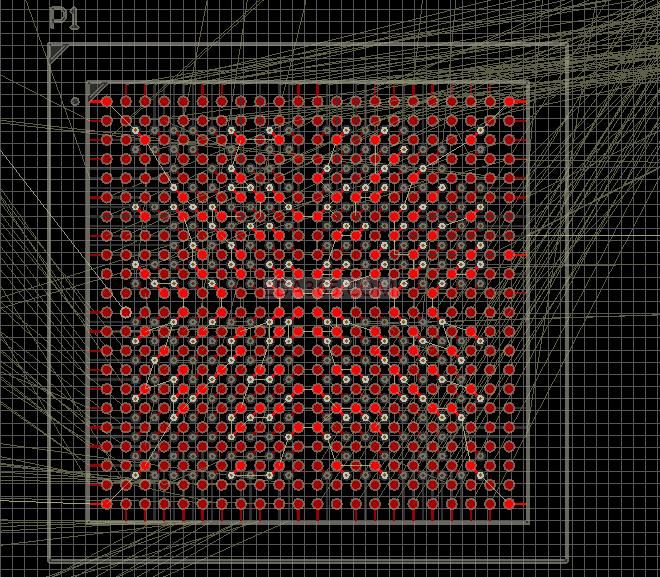

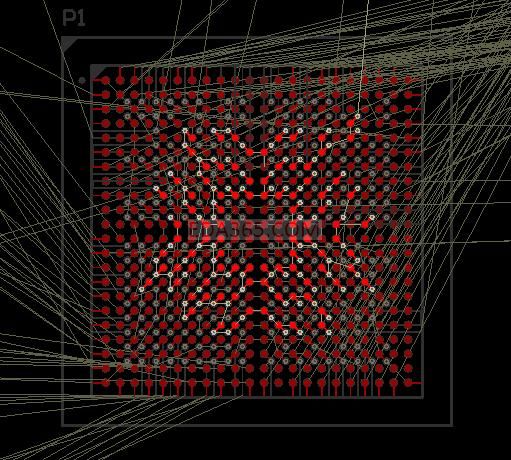

下图高亮的是地

这个图是1.2V 内核,另外还有3.3V IO和PLL电源。

1、现在看中间可以放置十字交叉的两排0603电容。其它的电容怎么办?只能放在外围?

2、还有就是PLL电源的电容这样就离的比较远了怎么办?

3、如果使用忙埋孔电源去耦能够更好么?可是我看还是放不下0603的0402的还有希望。

4、电源层我如果挖出一块1.2内核对于信号回流应该没有影响吧?

5、我这样安排叠层有什么问题么?还有更还的方法么?

6、哪位大侠有类似的去耦电容布局图可以给我参考一下?

准备用六层通孔板,叠层就是S1、G1、S2、P、G2、S3。

主要就是不知道电容怎么放置?

下图高亮的是地

这个图是1.2V 内核,另外还有3.3V IO和PLL电源。

1、现在看中间可以放置十字交叉的两排0603电容。其它的电容怎么办?只能放在外围?

2、还有就是PLL电源的电容这样就离的比较远了怎么办?

3、如果使用忙埋孔电源去耦能够更好么?可是我看还是放不下0603的0402的还有希望。

4、电源层我如果挖出一块1.2内核对于信号回流应该没有影响吧?

5、我这样安排叠层有什么问题么?还有更还的方法么?

6、哪位大侠有类似的去耦电容布局图可以给我参考一下?

有做过类似的帮下忙吧

正遇到类似问题

学习学习呀,