input coulpling capacitor in LNA

Any capacitor have a SRF (resonant frequency) and a parasitic inductance, that you have to take in consideration during your simulation.

Ideally is to use in your simulation the S parameters of the capacitor provided by the manufacturer.

Any RF active circuit needs coupling capacitors. but some LNA's having inbuilt coupling capacitors which may need a simple inductor circuit at the input for matching.

if not, as said above select the capacitors whose SRF is higher that your frequency of operation. change the position of coupling cap after the matching circuit and see.

negative gain sounds like circuit is not stable, check for stability also. keep ideal caps first and simulate the circuit and replace the ideal with capacitor models and optimize.

what do u mean by having inbuilt couplng cap?simple inductor circuit?r u referring to some L-matching n/w? ur answer is not very clear, plz if u can elaborate on it further. and have a look atthis ciruit, it doesnt have any coupling capacitor , so is this design okay?

http://www.ecti-thailand.org/assets/...235_pub_17.pdf

this isnt my circuit , but it also doesnt have any coupling capacitor

and negative gain occurs only after i add a coupling capactior, otherwise my circuit works perfectly..fully stable

see attached chip as caps inside.

sir, we are designing an LNA chip..by built in capacitor r u referring to an on chip capacitor? we already are referring to an on chip capacitor...

actually we are very basic level designers..designing LNA as a part of our university project..so we are very sorry if our questions seem irritating but it wil be a great help if u could guide us..cuz we are in a big fix over this issue

An input coupling capacitor blocks DC. On the other hand, in order to compensate such capacitor a series inductor is used, and it allows to set input operating frequency, but it depends on LNA topology. Which topology are you using?. For example, an inductive source degeneration topology allows to improve linearity and common-gate topology has better bandwidth.

see page 7 of link 1 document to avoid RF current getting grounded and to reduce noise due to a pole at the output a series inductor is used at input with out a coupling capacitor

from page 10 of link 2 document :Gate to source capacitance becomes significant and an inductor is used to nullify gate to source capacitance and use it for matching. so a coupling cap can be avoided for CMOS common gate LNA's.

the above are for CMOS cascode LNA designs only.

link1: http://citeseerx.ist.psu.edu/viewdoc...=rep1&type=pdf

link2: http://www.qsl.net/va3iul/LNA%20design.pdf

i am designing a distributed cmos casode lna from 0.1G to 2.7G problem is that when i add a coupling capacitor even in the basic distrbuted topology , gains s21 becomes negative.

---------- Post added at 17:17 ---------- Previous post was at 17:02 ----------

can coupling cap only be ignored in case of common gate? what about common source, im making distributed amplifer which is common source . whenever a capacitor is added even in the basic topology of distributed amplifer without any ither thing added , the gain is negative!

You mean in a simulation, with an ideal capacitor? Or how?

with ideal capacitor. and yes in simulation. im using cadence.

Complex S21 will be a negative value due to the circuit's phase reversal of course. Or are you referring to S21 magnitude (in db)?

s21's value in db, it gets -25dB , i tried changning the value of capacitor and did sweep analysis, the best value is like -20 dB

http://inst.eecs.berkeley.edu/~ee217...st_Amp_b+r.pdf check this out, they also havent used any coupling cap in their schematic which is in the end of document

In this case, I expect either insufficient transistor gm or output saturation. Did you determine gm? What is transistor Id?

Id is 5.4m for each transistor

I would expect a gm > 30 mmho (mS) for this Id value with Vgs of 1 V. It should be listed in the Cadence analysis. A gain of -20dB refers to a gm < 2, which sounds unlikely. So there must be some circuit error.

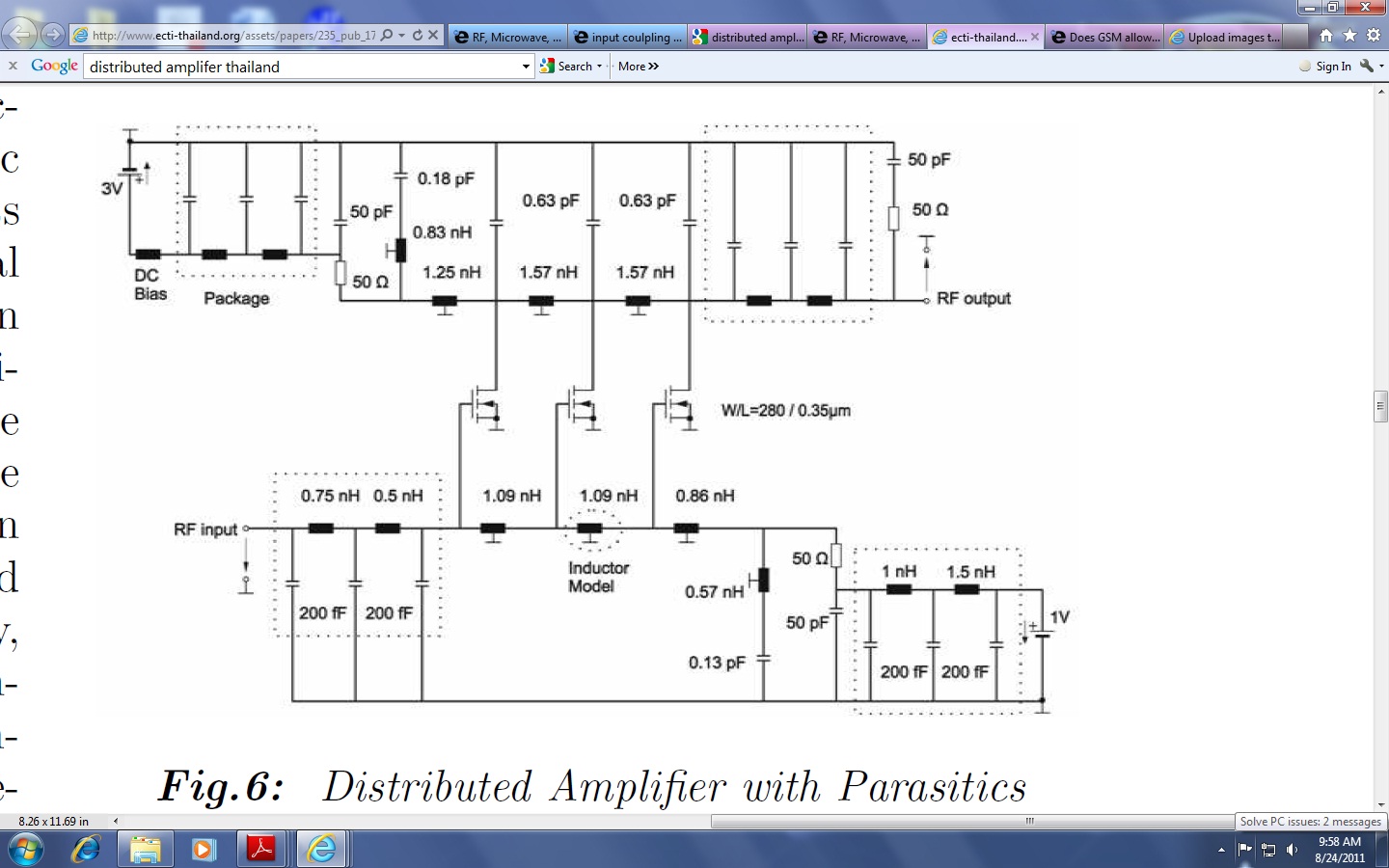

In circuit refereed as fig6, are parasitic losses included as if they were components. It is a symbolic signal schematic with 3 cap, 3 res and 3 transistors specified. It is a typical schematic where only parameters needed for RF simulation are included, not equal with a real circuit.

As there is no DC design, are these components not specified. Input/Output of this circuit can not be loaded by a DC load as that would affect DC bias.

Serial cap at input and output are therefore assumed as it is a DC voltage at these pins.

A serial cap at input, of any normal value, can not cause the problem you describe, at least not in this circuit. It is more likely related to simulation setup.

- Different Input/Output matching

- How do you choose input power while doing loadpull?

- Why an input inductor required in all GPS LNA?

- Input and output impedance matching in Distributed amplifier

- In distributed amplifiers, is it total input capacitance of the gain stage or Cgs

- curve fitting for input and output matching