Powerful learning approach: reverse engineering of microwave circuits from internet.

时间:04-05

整理:3721RD

点击:

In this thread i want to discuss microwave circuits from internet. It can be mixers, oscillators, filters, etc. - there are many amateur sites and tons of papers with design examples, that can be analyzed in many ways. So we can learn something new and check theory, even if somebody have no access to expensive measurement devices, such as network analyzers and spectrum analyzers. Using device parameters and other data given by authors, even layout photos, we can try to design the same device using our methods, software tools, and check how far our result differs from the original authors and discuss it. Additionnaly i want to recreate some of those circuits for lower frequency bands, to prove theory on practice. Maybe some students will get ideas about their final projects,etc.

I want to start from analyzing this paper: Quadruple-push oscillator (see preview available), then learn Octa-push oscillator. The good thing is that authors provide photos of their prototype boards, active device model and dielectric constant of laminate.

1. Starting from digging datasheet on active device:

Used FET transistor FHX35 (datasheet: www.qsl.net/n9zia/pdf/FHX35LG.pdf)

Frequency of oscillation: 8.95GHz. We can use S-parameters for 9GHz or interpolate between 8GHz and 9GHz. I will use 9GHz:

2. Obtaining millimeter lengths of microstrips.

Approximately lengths can be obtained using lead sizes of FHX35 transistor. Or we can use frequency, dielectric constant and size of microstrip resonator, but i prefer first way (see later why).

FHX35's width between leads (source to source or gate to drain) = 4.78mm

FHX35's diameter of ceramic part approximately = 1.78mm

Measuring size of this elements in pixels we can obtain scale coefficient and calculate lenghts of other parts:

Now we have approximate lenghts of some microstrips:

gate stub is 7.1mm, drain stub is 5.5mm, resonator side is 6.999=7mm.

Resonator full lenght is 7*4=28 [mm]

There is also short source stub, but it's configuration is unclear to me (short to ground only at one source lead). It will have effect on S-parameters of transistors, maybe it is inductive stub for increased instability. Anyways, we can try to add different inductance later to see if we can calculate the same Drain and Gate stub lenghts as in original design.

3. Trying to design the same microstrip layout using my little knowledge.

Dielectric constant Er of used laminate is 2.15.

I like to use online microstrip line calculator from this page: http://www1.sphere.ne.jp/i-lab/ilab/tool/ms_line_e.htm

Using this calculator, we obtain values:

effective Er = 1.879

lambda/4 = 6.08 mm

Using some formulas can

Here is first surprise: one-wavelength microstrip resonator length must be about 24.4mm long. If it is ring resonator shaped as square,

each side of it is about quater-wavelenght = 6.1mm

But in original design resonator lenght is about 28mm long, and quter-wavelength side of a square is 7mm.

Even if we calculate Er effective with 100 Ohm lines, quater-wave is 6.3mm, that is still far from 7mm.

Trying to do it another way. Resonator square size is about 82 pixels.

Resonant frequency is 8.95GHz

Er=2.15

Gate and drain stubs looks about 50 Ohm, and resonator line is thinner, maybe 25 Ohm.

Trying to get scale coefficient one more time:

Stubs:

Drain stub is 5.1mm, gate stub is 6.5mm.

4. Trying to calculate drain and gate stubs based on S-parameters of device and compare it with original design:

Stability coefficient is too high, because source stub not was taken into account:

I choosed reflection coefficients this way:

Gate and drain impedances can be realized using open stubs:

In original design drain stub is 5.1mm, gate stub is 6.5mm.

Ours: 6.3mm and 7.29mm.

After adding inductance stub, k becomed <0. But gate and drain stubs becomed longer than in original design: both> 10mm.

I am going to continue to analyze this circuit in next posts. Next logical step is to build script for searching reflection coefficients for original stub lenghts.

Results of my calculations vs original design:

gate stub = 7.3mm VS 6.5mm

drain stub = 6.3mm VS 5.1mm

Difference is about 1mm for each stub. Assuming source stub influence on S-parameters did not taken into account and pixel measurement erros, it is not so far from original result.

Let's try to add source stub. We can't see how microstrip goes under the FET. It can be whole quarter-wave microstrip line with short to GND on one side, or two separate stubs with one grounded. As separate grounded stub have inductive behaviour, i guess it is. Also it can be capacitive stubs? After playing with source stub it becomed obvious, that it's influence on gate and drain stub made them ever bigger, and far from original design. I am going to see original gate stub impedance on smith chart and see where it is:

gate stub is 6.5mm,

electrical length: 90*OriginalGateStub/pcbquarterwave = 91.8deg.

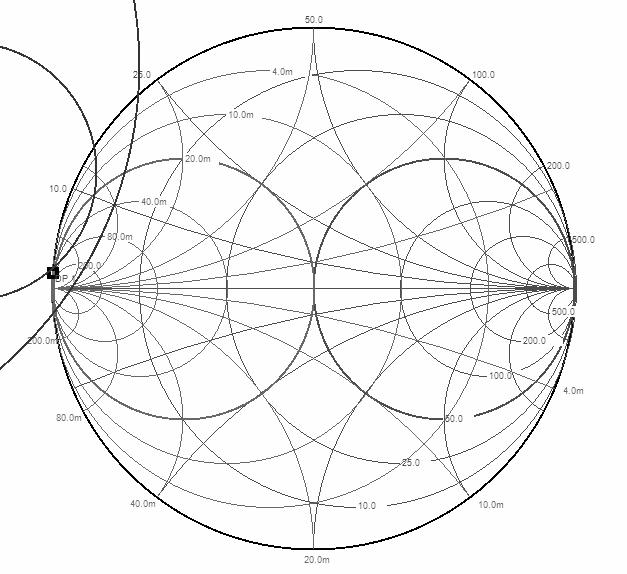

Gate impedance is 0+1.5i. On smith chart it is point DP1, near inside part of unstable input circle:

This point is almost the same, that was choosen in our calculations. Trying to use original gate stub reflection and recalculate drain stub gives no improvement. As we have enough freedom in choosing reflection coefficients, stub lenght variations are not so important. I think such scheme can be reproduced for lower frequency doubler/quadrupler this way: make negative resistance scheme: calculate reflection coefficients, add matching stubs for gate and drain (only match phase, so no additional stubs). DC-couple two equal oscillators to ring resonator. Source is grounded, without additional stubs.

I want to start from analyzing this paper: Quadruple-push oscillator (see preview available), then learn Octa-push oscillator. The good thing is that authors provide photos of their prototype boards, active device model and dielectric constant of laminate.

1. Starting from digging datasheet on active device:

Used FET transistor FHX35 (datasheet: www.qsl.net/n9zia/pdf/FHX35LG.pdf)

Frequency of oscillation: 8.95GHz. We can use S-parameters for 9GHz or interpolate between 8GHz and 9GHz. I will use 9GHz:

Code:

S11=PolarToRect(0.726,-153.8)S11 = -6.514095764e-1 - 3.205332491e-1i S12=PolarToRect(0.90,-15.3)S12 = 8.681016766e-1 - 2.37485745e-1i S21=PolarToRect(2.497,32.4)S21 = 2.10828683e0 + 1.337959507e0i S22=PolarToRect(0.468,-136.9)S22 = -3.417159455e-1 - 3.197721261e-1i

Approximately lengths can be obtained using lead sizes of FHX35 transistor. Or we can use frequency, dielectric constant and size of microstrip resonator, but i prefer first way (see later why).

FHX35's width between leads (source to source or gate to drain) = 4.78mm

FHX35's diameter of ceramic part approximately = 1.78mm

Measuring size of this elements in pixels we can obtain scale coefficient and calculate lenghts of other parts:

Code:

k=1.78/21k = 8.476190476e-2 ' or k=4.78/56k = 8.535714286e-2 drain_pixels=65drain_pixels = 6.5e1 gate_pixels=84gate_pixels = 8.4e1 resonator_side_pixels=82resonator_side_pixels = 8.2e1 drain_mm=k*drain_pixelsdrain_mm = 5.548214286e0 gate_mm=k*gate_pixelsgate_mm = 7.17e0 resonator_side_mm=k*resonator_side_pixelsresonator_side_mm = 6.999285714e0

gate stub is 7.1mm, drain stub is 5.5mm, resonator side is 6.999=7mm.

Resonator full lenght is 7*4=28 [mm]

There is also short source stub, but it's configuration is unclear to me (short to ground only at one source lead). It will have effect on S-parameters of transistors, maybe it is inductive stub for increased instability. Anyways, we can try to add different inductance later to see if we can calculate the same Drain and Gate stub lenghts as in original design.

3. Trying to design the same microstrip layout using my little knowledge.

Dielectric constant Er of used laminate is 2.15.

I like to use online microstrip line calculator from this page: http://www1.sphere.ne.jp/i-lab/ilab/tool/ms_line_e.htm

Using this calculator, we obtain values:

effective Er = 1.879

lambda/4 = 6.08 mm

Using some formulas can

Code:

C=299792458C = 2.99792458e8 Ereff=1.88Ereff = 1.88e0 lambda=1000*C/(Freq*Sqrt(Ereff))lambda = 2.442973427e1 lambda/4Ans = 6.107433567e0

each side of it is about quater-wavelenght = 6.1mm

But in original design resonator lenght is about 28mm long, and quter-wavelength side of a square is 7mm.

Even if we calculate Er effective with 100 Ohm lines, quater-wave is 6.3mm, that is still far from 7mm.

Trying to do it another way. Resonator square size is about 82 pixels.

Resonant frequency is 8.95GHz

Er=2.15

Gate and drain stubs looks about 50 Ohm, and resonator line is thinner, maybe 25 Ohm.

Trying to get scale coefficient one more time:

Code:

Freq=8.95 * 10^9Freq = 8.95e9 Er=2.15Er = 2.15e0 W=0.7W = 7e-1 h=0.8h = 8e-1 Ereff=(Er+1)/2+ ((Er-1)/2)*((1+12*h/W)^-0.5+0.04*(1-W/h)^2)Ereff = 1.725258208e0 ' in millimeters lambda=1000*C/(Freq*Sqrt(Ereff))lambda = 2.550178714e1 lambda/4Ans = 6.375446785e0 pixels=82pixels = 8.2e1 k=(lambda/4)/pixelsk = 7.774935104e-2 ' then diameter of FET in pixels must be about 23 pixels: FETpix=1.78/kFETpix = 2.289408177e1

Code:

drain_pixels=65drain_pixels = 6.5e1 gate_pixels=84gate_pixels = 8.4e1 resonator_side_pixels=82resonator_side_pixels = 8.2e1 drain_mm=k*drain_pixelsdrain_mm = 5.053707818e0 gate_mm=k*gate_pixelsgate_mm = 6.530945488e0 resonator_side_mm=k*resonator_side_pixelsresonator_side_mm = 6.375446785e0

4. Trying to calculate drain and gate stubs based on S-parameters of device and compare it with original design:

Stability coefficient is too high, because source stub not was taken into account:

Code:

delta=S11*S22-S12*S21delta = -2.027854201e0 - 3.429628754e-1i k=(1-Abs(S11)^2-Abs(S22)^2+Abs(delta)^2) / (2*Abs(S12*S21))k = 9.975784711e-1

Code:

Gs=1/S11Gs = -1.235893071e0 + 6.081347835e-1i Amp=Abs(Gs)Amp = 1.377410468e0 Ang=Arg(Gs)Ang = 1.538e2 Gs=PolarToRect(Amp*0.9,Ang)Gs = -1.112303764e0 + 5.473213051e-1i Gout=S22+(Gs*S12*S21)/(1-S11*Gs)Gout = -2.785016695e1 + 4.086367848e0i Zs=50*(1+Gs)/(1-Gs)Zs = -5.636804823e0 + 1.149499532e1i Zs=i*Im(Zs)Zs = 1.149499532e1i Zload=50*(1+Gload)/(1-Gload)Zload = 4.660198712e1 - 4.812981015e-1i Zload=0*Re(Zload)/3+i*Im(Zload)Zload = -4.812981015e-1i

Code:

GateStubAns = 7.292612722e0 DrainStubAns = 6.336378758e0

Ours: 6.3mm and 7.29mm.

After adding inductance stub, k becomed <0. But gate and drain stubs becomed longer than in original design: both> 10mm.

I am going to continue to analyze this circuit in next posts. Next logical step is to build script for searching reflection coefficients for original stub lenghts.

I found error in typing S12 S-parameters, it must be:

Code:

S11=PolarToRect(0.726,-153.8)S11 = -6.514095764e-1 - 3.205332491e-1i S12=PolarToRect(0.090,-15.3)S12 = 8.681016766e-2 - 2.37485745e-2i S21=PolarToRect(2.497,32.4)S21 = 2.10828683e0 + 1.337959507e0i S22=PolarToRect(0.468,-136.9)S22 = -3.417159455e-1 - 3.197721261e-1i

gate stub = 7.3mm VS 6.5mm

drain stub = 6.3mm VS 5.1mm

Difference is about 1mm for each stub. Assuming source stub influence on S-parameters did not taken into account and pixel measurement erros, it is not so far from original result.

Let's try to add source stub. We can't see how microstrip goes under the FET. It can be whole quarter-wave microstrip line with short to GND on one side, or two separate stubs with one grounded. As separate grounded stub have inductive behaviour, i guess it is. Also it can be capacitive stubs? After playing with source stub it becomed obvious, that it's influence on gate and drain stub made them ever bigger, and far from original design. I am going to see original gate stub impedance on smith chart and see where it is:

gate stub is 6.5mm,

electrical length: 90*OriginalGateStub/pcbquarterwave = 91.8deg.

Code:

elen=90*6.5/lambda4elen = 9.17582751e1 Zgate=-i*50*(1/Tan(elen))Zgate = 1.534866322e0i

This point is almost the same, that was choosen in our calculations. Trying to use original gate stub reflection and recalculate drain stub gives no improvement. As we have enough freedom in choosing reflection coefficients, stub lenght variations are not so important. I think such scheme can be reproduced for lower frequency doubler/quadrupler this way: make negative resistance scheme: calculate reflection coefficients, add matching stubs for gate and drain (only match phase, so no additional stubs). DC-couple two equal oscillators to ring resonator. Source is grounded, without additional stubs.