(Understanding) Problem: Load-Pull in Cadence/Virtuoso

if I understand this right, then Load-Pull means, that a load with a tunable impedance is connected to the output of a circuit (for example an amplifier). Then this impedance is varied and the power which is delivered to this load is observed. If this power is at its maximum, the corresponding impedance is the complex conjugated of the output-impedance of the actual circuit (the amplifier). Is this right?

The same method should work to find the input-impedance of a circuit (Source-Pull?).

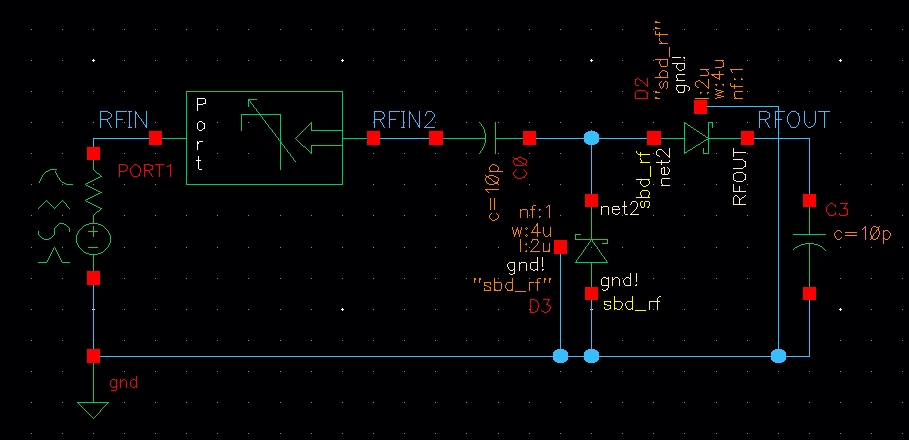

I read in the "SpectreRf Workshop" PDF about "Power Amplifier Design Using SpectreRf" the chapter about "Load-Pull Measurements". I simulated the example circuit and everything was fine.

My goal is to find the input-impedance of a simple rectifier (the impedance, at which the output-DC-voltage is at its maximum).

This is the analyses form:

And this is the properties form of the port:

The variables:

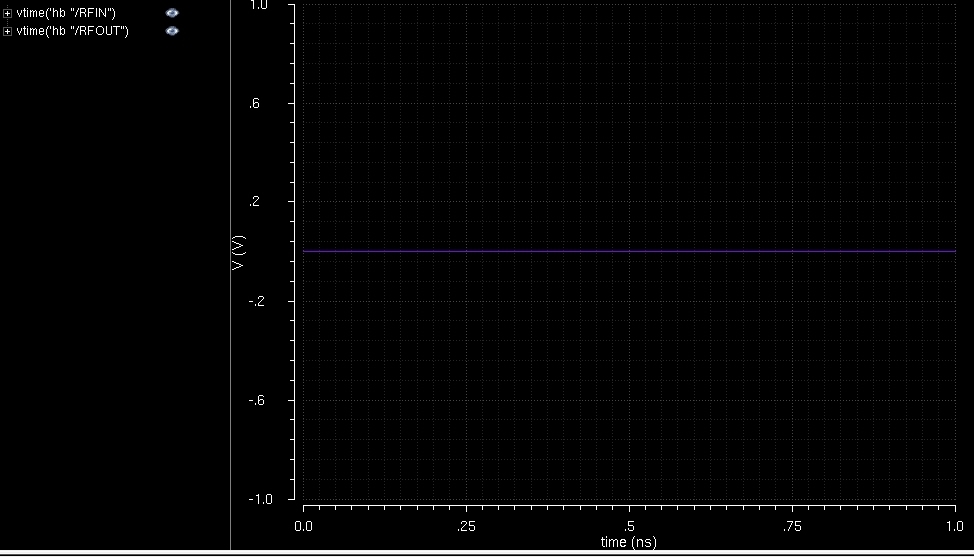

If I do a normal hb- oder pss-simulation (normal means: no load-pull) the simulation results are as expected.

But with activated load-pull, the port delivers always 0 W (RFIN is in the order of E-171 V).

What am I doing wrong?

I tested this with only an inductor instead of the rectifier. Same result: without load-pull everything is fine, with load-pull everything is zero.

Additional question: Can anyone explain me, why I have to fill in 50 Ohm? At 3 places: Z0 in the analyses form, resistance in the port-properties, r0 in the variables. I thougt, that the impedance is varied. But where are these 50 Ohms used?

Please help me!

Thank you!

Sascha

Right.

Correct.

Show me Spectre's netlist.

If you don't use r0, you don't have to define r0 as design variable.

As far as you do load-pull correctly, resistance in the port-properties will be ignored.

Z0 in the analyses form is actually used in Z0 in load-pull analysis.

The impedance which you have found by applying Load-Pull technique is NOT the complex conjugate of the output impedance of actual circuit.Optimum impedance is generally pretty different than complex conjugate of the output impedance of the circuit.Load Pull technique is very useful for Power Amplifiers and it's generally measured and simulations are pretty far from the reality due to model inconsistencies,uncertainties and rough model approximations.

I guess you're trying to find Input and Output Impedances under large signal conditions.In order to do this, you may try some simulation techniques such as PSS, HB or LSSP.They will give you a right aspect for your circuit.

Code dot - [expand]

The r0 variable was defined in the SpectreRf Workshop Example. It is indeed unnecessary.

This I don't understand. Where is this Z0 needed during the load-pull simulation? Is it maybe only needed as scaling factor for the smith-charts?

I have to design a rectifier which acts as power source for a RFID-Transponder. The circuit in the picture in my first post was a simplification. Until now I used pss-simulations and different calculations to determine the impedance of the rectifier. For example Ohm's law:

harmonic(((-1 * vh('pss "/port0_plus")) / ih('pss "/PORT0/PLUS")) 1)

Or I used the magnitudes and phases of the input voltage and current:

complex(((ymax(vtime('pss "/port0_plus")) / ymax((-1 * itime('pss "/PORT0/PLUS")))) * cos((harmonic((phaseRad(vh('pss "/port0_plus")) - phaseRad(ih('pss "/PORT0/PLUS"))) 1) + pi))) ((ymax(vtime('pss "/port0_plus")) / ymax((-1 * itime('pss "/PORT0/PLUS")))) * sin((harmonic((phaseRad(vh('pss "/port0_plus")) - phaseRad(ih('pss "/PORT0/PLUS"))) 1) + pi))))

The impedance value is needed to design an antenna for the RFID-Transponder. But I think, that a impedance matched system is not optimal. A larger R in the antenna results in a larger voltage amplitude, which is better for the diodes. I want to test, if this leads to an higher DC-Voltage at the output of the rectifier. I tried to use a simple variable sweep to run pss-simulations with different R-values. But many of these simulations didn't run because of converge problems. Therefore I thought, that the load-pull-method is better to simulate the rectifier with different impedances in the port (which acts as an equivalent for the antenna).

I hope you understand what I am trying to say (sorry for my bad english)!

I have an additional question:

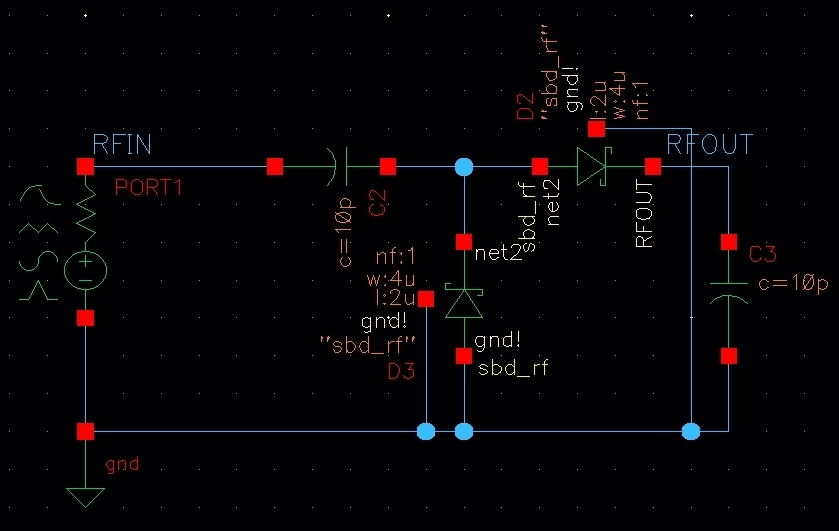

In the "SpectreRf Workshop" PDF about "Power Amplifier Design Using SpectreRf", in the chapter about "Load-Pull Measurements" they simulated this circuit:

[from https: // stra . to /ap/9QlOaYtv/s/ b0fb15d06cd893ac5a9e392cd8fe5e12/ example.jpg[/IMG]

In the Analyses-Form, PORT2 is the used Load Instance.

But in the Properties-Form of PORT2, "dc" is choosen as "Source Type". Why?

PORT1 is "sine". That means, that RFIN is a sine-signal and therefore RFOUT is also a sine-signal.

Why is PORT2 not "sine" as "Source Type"?

I am confused!

Wrong.

How do you measure an output impedance ?

S22 of LSSP or S22 of VNA(Vector Network Analyzer) at large signal drive level can never be appropriate for actual operation, since these are evaluated by reverse direction driving.

There is no direct method to measure output impedance at forward driving condition.

LoadPull is actually used for estimating output impedance even in actual measurement using actual instruments.

Can you understand a definition of S22 in LSSP ?

This can never be appropriate for actual operation, since it is evaluated by reverse direction driving.

PSS is a generic name which means both HB and Shooting-Newton.

And LSSP is no more than PSS.

LoadPull simulation is also PSS.

Can you understand LoadPull Simulation ?

It is no more than PSS such as HB or Shooting-Newton.

So such issues are true for any simulation techniques.

Important point is a driving direction.

LSSP is a reverse driving.

On the other hand, LoadPull is a forward driving direction.

BTW, S22 of PSS/PSP in Cadence Spectre give small siganl S22 at forward large signal driving.

OK, I understood why LoadPull is the better method to determine the output impedance than simulating or measuring Large Signal S22. But what about my problem regarding the simulation of the input impedance? Why is RFIN (nearly) 0 V?

And why is a DC-type PORT used at the output in the Spectre example?

No.

Z=Z0*(1+Gamma)/(1-Gamma), Here Z can be Zload or Zsource

Gamma=rho(Z)*exp[j*phi(Z)]

So Z0 is needed to determine Z.

Notations in GUI of Cadence ADE are improper or wrong.

rho(Z) and phi(Z) should be corrected to rho(Gamma) and phi(Gamma).

It is because PORT2 is load.

Driving direction of Loadpull is forward not reverse.

Right.

Wrong.

It is because PORT2 is load.

Driving direction of Loadpull is forward not reverse.

Your previous goal is different from the following.

You should do SourcePull Simulation.

Correct.