Hspicerf trannoise setup for PLL simulation

时间:04-04

整理:3721RD

点击:

hey man

I am a beginner of PLL design. Here I have a problem about how to setup the .trannoise parameters to measure the jitter. Would anyone share your experience about the setup of trannoise? Thank you very much.

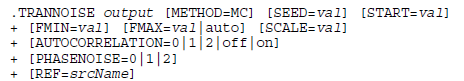

My PLL design has 200MHz output frequency. Following the format in hspice manual showing below, I'm curious about how to determine the value of "seed", "SCALE", "FMIN" and "FMAX".

About the FMAX, I have noticed that the manual suggest to 2*highest frequency of circuit. Why is that?

BR

CH

I am a beginner of PLL design. Here I have a problem about how to setup the .trannoise parameters to measure the jitter. Would anyone share your experience about the setup of trannoise? Thank you very much.

My PLL design has 200MHz output frequency. Following the format in hspice manual showing below, I'm curious about how to determine the value of "seed", "SCALE", "FMIN" and "FMAX".

About the FMAX, I have noticed that the manual suggest to 2*highest frequency of circuit. Why is that?

BR

CH

You don't have to set "seed" and "SCALE".

If you don't specify "FMIN", "FMIN" is setted to "FMAX".

So if you would like to include low frequecy noise more accurately, set "FMIN"

Basic Sampling Theory.

Hi!

Thanks for your reply

Here I have a DAC with 6MHz frequency clock. The band-of-interest is about 100kHz.

In this case, should FMAX be set to 12MHz or 200kHz ?

Furthermore, what is the physical meaning of "seed" ?

Thanks!

BR

CH

fmax = 2*10*6MHz = 120MHz

"seed" is a seed of random number generator.