CYCLONE II系列FPGA上DDR SDRAM数据接口设计

FPGA内部DDR接口实现

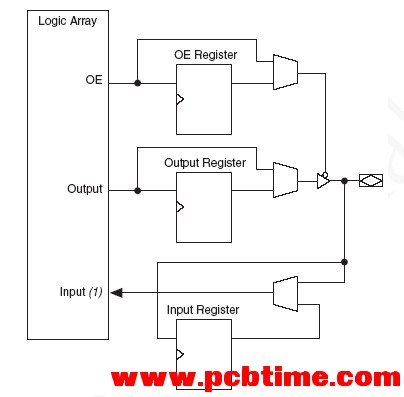

图 1 FPGA内部DDR接口实现

在DDR SDRAM接口中,地址、控制线均采用SDR的模式,以DDR参考时钟的上升沿为参考。与此相对,DQS/DQ/DM构成了DDR SDRAM接口的数据通道,其中DQS为参考,可看作时数据通道的参考时钟,DQ/DM为DDR模式,以DQS的上升和下降沿作为参考,每个时钟周期采样两次。DQS/DQ/DM均为双向信号,在写操作,FPGA为输出,在读操作,FPGA为输入。FPGA内部实现的DDR DQ/DQS接口如图 1所示。其中分为2个部分:DQS和DQ。在我们的设计中一般将采用8或16位的DQ分组,每组以一个DQS作为参考。这里只讨论单根DQ的情况。

首先考虑输出的情况。在写操作中,DQS和DQ均处于输出状态,此时,DQS和DQ的输出均由PLL产生的控制器主时钟产生,为了保证在DDR SDRAM接口初采样正确,在FPGA内部PLL输出了2路时钟,采用一路0°相移时钟产生DQS,采用另一路–90°相移时钟产生输出数据。在输出接口处采用二选一电路分别在上升沿和下降沿产生DQS和DQ。图 2显示了在一个2周期burst写操作的波形,通过采用–90°相移将DQS的沿对其到数据的中间位置,以保证DDR SDRAM的正确采样。

图 2 FPGA写DDR操作输出信号时序

在输入电路方面,DDR SDRAM接口输出的数据波形参见图 3。DDR SDRAM输出的DQS和DQ信号是对齐的,在FPGA内部接收电路对DQ的采样是以DQS为参考的,考虑到寄存器的采样时序要求,需要将DQS进行移相处理,理想情况下达到90°相移,以保证可靠的内部采样。

图 3 DDR SDRAM输出数据时序

FPGA内部对于DQS和DQ在输入部分的实现参见图 1。为了将DQS作为DQ内部采样的参考时钟,通过2个部分实现:首先使用IOE内的可调延迟电路(Clock Delay Control Circuitry),对DQS输入进行移相操作,其次,通过使用时钟控制电路(Clock Control Block)将延迟后的DQS放到高速时钟网络(Global Clock)上,保证对相同DQS group内的所有接口进行采样。DQ部分的采样电路如图 4所示。电路输出时序参见图 5。经过延迟和反向的DQS作为参考时钟分别提供给三个LE内的寄存器,DQ输入经过DQS采样和延迟后,形成2-BIT宽的数据输出。由于DQS与内部的系统时钟分处不同时钟域,采样后信号在提供给内部逻辑使用之前,需要通过2个同步寄存器同步到系统时钟域内,经系统时钟同步后生成dataout_h和dataout_l。

图 4 DQ输入采样电路

图 5 DQ输入采样电路时序

DDR接口实现约束方法

在FPGA内部,所有的引脚通过IO BLOCK连接到内部的资源上,每个IO BLOCK内有多个IOE,每个IOE对应一个引脚。在CYCLONE II系列中每个IOE的基本结构参见图 6。每个IOE内有1个输出寄存器、1个输出使能寄存器、一个输入寄存器。对于一般的SDR高速同步接口,可以使用IOE内的寄存器实现输入信号在IOE内的直接采样,或者输出信号在IOE内的同步输出,以使接口信号具有比较良好且稳定的外部时序特性。这是一个非常重要的功能,但是要实现这种功能要满足的前提条件是在引脚上的网络上不能有组合逻辑的出现,否则软件会将引脚信号作为逻辑连线连接到内部资源而不使用IOE内的寄存器。在DDR数据接口的设计中,从图 1中可见,DQ接口在输入输出部分都使用了组合逻辑,这样,就导致无法使用IOB内部的寄存器资源,必须在内部资源(LE)中实现接口逻辑。对于DQ输出接口来讲,由于内部实现了DQS相移,其时序相对宽松,从我们实际使用和信号测量的结果来看,时序不会出现问题,但是对于输入接口来讲,由于内部存在三级采样,因此采样的时序要求较高,要求我们在DQS域内进行处理时要具备比较稳定的布线结果,保证充分的采样和保持裕度。

图 6 CYCLONE II系列FPGA IOE结构

CYCLONE II系列FPGA内IOB和内部资源之间的关系参见图 7。每个IOB内的各个IOE可以连接到IOB内的局部连线资源,也可以连接到FPGA内部的行和列布线资源上,同时,对于行IOB来讲,具备一组到内部相邻LAB的直接链路(direct link),这是我们在实现DDR数据接口输入时需要使用的最重要资源。FPGA内部的LAB结构参见图 8。在每个LAB中有16个LE,每个LE中有一个查找表和一个寄存器,并且查找表和寄存器可以相互独立使用,在一个LAB内部的寄存器之间还存在级联用的直接连线,可以用于实现移位寄存器。从DDR接口的实现电路可见,接口的采样部分以寄存器为主,逻辑很少,因此可以充分使用相邻LAB内的资源。们对于软件的控制,不能将所有的布线工作都由软件自动完成。

在ALTERA提供的DDR SDRAM控制器的IP CORE中,对于FPGA内的资源的使用进行了限定,因此可以达到较高的性能,但是在我们的设计中,DDR接口的数据通路部分是采用源码的方式进行设计的,在综合时,为了能够利用这些资源,必须进行约束。这里需要采用的约束方式是进行LOCATION约束,对于每个DQ接口来讲,需要进行5个寄存器的LOCATION约束,限制其使用的LAB。在约束了LOCATION后,软件可以使用内部的direct link进行最短的布线,保证实现比较稳定快速的DQ接口。

从采用QUARTUS II 5.1和6.0进行的实际布线情况来看,在不采用LOCATION约束的情况下,会出现两种情况:

? 在不采用任何约束的情况下,DDR接口的布线情况在不同的编译和设计中具有很大的离散性,当芯片的资源利用率达到一定的程度时,任何小的修改(即使与DDR接口无关),都会导致DDR接口时序出现变化,其表现为一根或几根DQ引脚上的延迟整体异常、上升沿和下降沿采样寄存器延迟差异较大等,导致数据读写的异常。

? 在采用DELAY时序约束的情况下,软件在不能满足延迟时序要求的情况下,只是给出告警,并忽略不能实现的约束,并不会严格保证时序满足。在这个过程中,即使约束都能够满足,因为没有量化的指标来确定延迟的具体范围,导致引脚之间仍然可能出现较大的差异,因为我们是采用DQS延迟来对一组内的所有信号进行采样,在各路延迟较大的情况下,是很难进行DQS延迟的确定的。

图 7 IOB和内部资源之间的关系

在进行DDR管脚分配时,芯片的引脚定义给出了参考引脚的定义方式,从布线结果的分析来看,这种推荐的引脚分配方式可以使每个IOB内只有最多3个DDR的DQ引脚,从DDR接口的实现来看,每个DQS域内有三个寄存器对应一个引脚,因为我们希望使用相邻的LAB来实现输入采样,这种分配方式保证了相邻的LAB内有足够的资源可以用于实现DDR输入采样。因此,我们在DDR引脚分配的时候要严格遵循推荐的引脚分配方式。另外,由于列IOB内不具有与相邻LAB之间的directlink,建议尽量采用行IOB实现DDR数据接口。LOCATION约束的指定方法:

? 在QUARTUS II 5.1或6.0软件中,打开assignment editor;

? 在category列表中,选择ALL-location-LAB;

? 在edit页面中输入需要的约束,需要指定的域包括:寄存器(在to栏中点击右键,在find node中查找),X coordinate 和Y coordinate。

? 对于所有的DQ引脚需要对下列几个寄存器进行约束:

? Input_cell_l

? Input_cell_h

? Input_latch_l

? Resynched_data_l

? Resynched_data_h

其中前三个寄存器用于DQS域中的采样,需要定义在IOB的相邻LAB内,后两个寄存器用于向内部时钟域的同步,需要定义在前者的相邻LAB内。以行IOB为例,假设某个引脚位于IOB_Xn_Yn内,需要将前三个寄存器约束在LAB_Xn-1_Yn内,将后两个寄存器约束在LAB_Xn-2_Yn内。

图 8 LAB结构

在进行了LOCATION约束,即使不进行delay约束,但是由于direct link的存在,布线的结果仍旧可以很好地满足我们的要求,DQ引脚以及各寄存器之间的延迟特性具备很好的稳定性,延迟特性非常理想。下表针对同一设计在约束前后的布线结果进行了比较。从表中的结果可见,约束后无论在绝对延迟和线间误差等方面,采用约束的结果明显要好于不进行约束的情况。除了DQ线延迟特性的改善外,由于延迟的DQS线被限制在接口相邻的LAB内走线,DQS(采样时钟)到各寄存器的延迟特性也具有很强的一致性,为进行DQS延迟约束的调整建立了良好的先决条件。

DDR接口时序设计和验证

从图 4和图 5可见,为了正确的实现输入采样并且向内部时钟域的同步,需要在3点保证正确的采样和保持时间:

? Input register A1,DQS负沿,通过DQS与DQ之间延迟保证

? Input register B1,DQS正沿,通过DQS与DQ之间延迟保证

? Sync_reg_h和Sync_reg_l,resync_clk正沿,通过DQS负沿与resync_clk之间延迟保证

DQS域时序设计

为了保证前2项采样的正确,需要考虑DDR SDRAM和FPGA的时序特性。DDR SDRAM(以HY5DU2841622E为例,工作在100MHz)和FPGA(EP2C35)的参数:

? Clock Half Period(tHP) 4.5ns

? Data Hold Skew Factor(tQHS) 0.75ns

? DQS-Out edge to Data-Out edge Skew(tDQSQ) 0.6ns

? Data valid window(tDW = tHP-tQHS-tDQSQ) 3.15ns

? DQS-DQPCB走线误差 (tskew) 0.1ns

? FPGA内部寄存器间DQS走线误差(tDQS_SKEW_ADDER) 0.05ns

? FPGA内部寄存器建立时间(LE_TSU) 0.05ns

? FPGA内部寄存器保持时间(LE_TH) 0.3ns

除上述参数外,我们还需要获取DQS和DQ到相应的采样寄存器位置的延迟信息,这些延迟信息在进行时域分析之前可以在assignment editor里面通过给相应的引脚添加report delay约束产生列表,需要获取下列信息:

? DQS-input_cell_l延迟

? DQS-input_cell_h延迟

? DQ-input_cell_l延迟

? DQ-input_cell_h延迟

在经过前面所介绍的DQ引脚及相应的寄存器位置锁定之后,DQ-input_cell_l和DQ-input_cell_h基本保持一致,并且DQ之间的延迟基本相同,另外DQS-input_cell_l和DQS-input_cell_h误差保持在tDQS_SKEW_ADDER内,可使用此参数直接计算误差。这样,对于某一组DQS-DQ,我们可以用某一个DQ上的一组数据参与运算:

? DQS-input_cell_l延迟(Tdqs_delay)

? DQ-input_cell_l延迟(Tdq_delay)

如果需要在各种不同速率等级的芯片上运行同样的程序,需要针对不同的芯片提取除上述参数。

读采样建立时间的计算:

T_Earliest_clock = Tdqs_delay - tDQS_SKEW_ADDER

T_Last_Data_Valid = tDQSQ + Tdq_delay

Tsetup_margin = T_Earliest_clock - T_Last_Data_Valid - LE_TSU - tskew

读采样保持时间的计算:

T_Latest_clock = Tdqs_delay + tDQS_SKEW_ADDER

T_Earliest_Data_Invalid = tHP-tQHS + Tdq_delay

Thold_margin = T_Earliest_Data_Invalid - T_Latest_clock - LE_TH - tskew

上述计算结果应保证:

? 0<Tsetup_margin< tDW;

? 0<Thold_margin< tDW

以HY5DU2841622E DDR SDRAM和EP2C35 FPGA为例,工作在100MHz下,DQS延迟线参数设置为38,通过对DQ引脚进行约束后,进行布线,并提取布线结果时间信息进行计算,以上各数据为:

? Tdqs_delay = 4.066ns

? Tdq_delay = 1.821ns

? T_Earliest_clock = 4.066ns - 0.05ns = 4.016ns

? T_Last_Data_Valid = 0.6ns + 1.821ns = 2.421ns

? Tsetup_margin = 4.016ns - 2.421ns - 0.15ns = 1.58ns

? T_Latest_clock = 4.066ns + 0.05ns = 4.116ns

? T_Earliest_Data_Invalid = 4.5ns - 0.75ns + 1.821ns = 5.571 ns

? Thold_margin = 5.571ns - 0.4ns - 4.116ns = 1.055ns

对于不同的DQS延迟参数设置,Tdqs_delay会有不同,我们可以通过改变延迟参数,来获得比较满意的Tsetup_margin和Thold_margin。可以采用如下做法:

? 将DQS延迟设置为最小值;

? 布线并提取结果计算Tsetup_margin和Thold_margin;

? 根据Tsetup_margin和Thold_margin计算需要的DQS延迟;

? 调整DQS延迟线参数,重新布线;

? 提取新的布线结果并计算验证。

由于DQS延迟线参数为静态设置,并且存在于IOE中,对于DQS延迟线参数的修改不会影响到其他布线的结果,因此,对于DQS延迟线的调整是可靠的。

DQS-SYS域同步时序设计

从图 4和图 5可见,经过DQS时钟域的采样之后,需要采用2个寄存器将采样输出(此时已经在DQS域内调整为对其的DQS下降沿的2个信号)同步到内部的时钟域上。一般来讲,为了在内部采用同步设计,我们直接采用DDR控制器或者系统时钟来进行同步操作,此处以SYS来代表内部的时钟域。

在进行DDR接口的时序设计时,我们采用的是由FPGA提供DDR SDRAM参考时钟的方式,因此,在同步到内部时钟域上时,我们要考虑整个时钟环路的延迟模型。参见图 9。其中register B为同步寄存器,采用SYS时钟(clk)作为参考,register A为DQ采样寄存器,采用经延迟反相的DQS作为时钟参考。

图 9 DDR时钟路径延迟模型

整个时钟路径包括下列部分:

? tPD (clk to pin) A-B两点间延迟,DDR输出接口延迟

? tPD (Clock Trace) B-C两点间延迟,PCB走线延迟(clk)

? tDQSCK(Read) C-D两点间延迟,DQS输出延迟

? tPD (DQS Trace) D-E两点间延迟,PCB走线延迟(DQS)

? tPD (Capture) E-G两点间延迟,DQS内部调整延迟

? tCQ (Capture) G-H两点间延迟,采样寄存器输出延迟

? tPD (Capture) H-I两点间延迟,采样输出传输延迟

整个延迟路径收到上述7项的影响。针对于具体的设计,这些数据从DDR手册和布线结果获得,布线时间参数的提取与前面介绍的方法类似,在编译报告的时间列表窗口中选中项相应的寄存然后点击右键选择“list path”选项,列出相关的所有时间参数,从中选择所需的数据:

? tPD (clk to pin) 4.43ns

? tPD (Clock Trace) 0.5ns

? tDQSCK(Read) +/-0.8ns

? tPD (DQS Trace) 0.5ns

? tPD (Capture) 4.066ns

? tCQ (Capture) 0.602ns

? tPD (Capture) 0.77ns

除计算上述参数外,针对不同的cas latency时间需要在tCQ (Capture)上进行调整,如果是采用整数周期的cas latency,需要在上述时间上增加1/2时钟周期的额外延迟(因为采样输出对齐在DQS的下降沿上),如果采用1/2整数周期的cas latency,则需直接使用上述计算结果。除上述调整外,在上述 时间内还需考虑时钟输出的占空比(会影响DQS输出延迟),我们可以通过控制CKP和CKN的布局和布线来得到比较理想的占空比,因此这里我们不考虑它的影响。

综合考虑上述各项因素之后,我们可得到的时延特性为:

? 2.5 cas latency 最大11.668ns 最小10.068ns

? 2 cas latency 最大16.668ns 最小15.068ns

经对上述数据按照DDR时钟周期取模数计算之后,可得相对于时钟上升沿的相位特性,可根据此计算结果来决定采用的CAS latency参数,以及PCB走线的约束。在上述设计中,我们选取cas latency参数为2,可以较好地满足我们的同步要求。

建议的设计方法

综合上述计算过程,对于DDR类的数据接口,建议的设计过程为:

1. DQ/DQS引脚锁定LOCATION

2. DQ采样相关寄存器位置锁定LOCATION

3. DQS延时设置为0和最大,进行布线

4. 按照布线结果计算DQS域内采样的建立和保持时间裕度,据此调整DQS延迟线参数

5. 进行布线

6. 按照布线结果提取时钟延迟特性,进行计算

7. 根据计算结果选择DDR SDRAM控制器的cas latency参数,并进行单板布线约束

8. 在进行PCB板布线是,建议对DQ和DQS线进行等长处理。

总结

在实现FPGA设计的过程中,我们通常需要注意两个方面的问题:时间特性和功能特性。一般来讲,我们大多采用同步设计方式,通过将寄存器之间的逻辑规模控制在一定的大小来确保时序的正确,并且可以通过最后布线结果的报表来判断是否能够满足运行频率的要求。由于基于这种假设,通常并不重视进行时域分析,但是在类似于DDR这类接口电路,以及在相同频率不同相位的域之间进行同步操作时(可能由于内部时钟走线延迟造成,一个全局时钟网络可能会出现几个ns的延迟),还是需要认真进行时域参数分析的。对于逻辑设计我们可以通过各种仿真软件来确保正确,但是如果时序正确这个前提条件不能满足,那么任何其他工作都是没有意义的,这是我们在今后的工作中需要特别注意的。同时,进行认真的时间分析可以有助于我们改进设计的性能,应该逐步增加我们对于软件的控制,不能将所有的布线工作都由软件自动完成。 在实现FPGA设计的过程中,我们通常需要注意两个方面的问题:时间特性和功能特性。一般来讲,我们大多采用同步设计方式,通过将寄存器之间的逻辑规模控制在一定的大小来确保时序的正确,并且可以通过最后布线结果的报表来判断是否能够满足运行频率的要求。由于基于这种假设,通常并不重视进行时域分析,但是在类似于DDR这类接口电路,以及在相同频率不同相位的域之间进行同步操作时(可能由于内部时钟走线延迟造成,一个全局时钟网络可能会出现几个ns的延迟),还是需要认真进行时域参数分析的。对于逻辑设计我们可以通过各种仿真软件来确保正确,但是如果时序正确这个前提条件不能满足,那么任何其他工作都是没有意义的,这是我们在今后的工作中需要特别注意的。同时,进行认真的时间分析可以有助于我们改进设计的性能,应该逐步增加我们对于软件的控制,不能将所有的布线工作都由软件自动完成。