PCB设计周中的数学计算

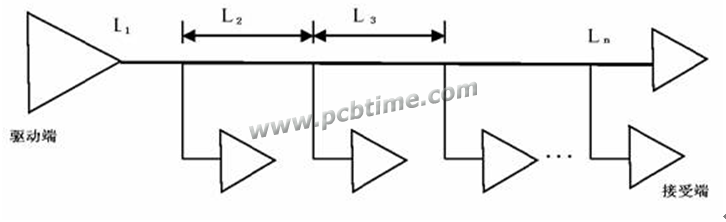

下图为PCB板上的一条内存地址总线电路.

给出条件:

1.图中n=8,其中L1=L2=…=L8=1 inch;图中的传输线长度只考虑此8段,其他不考虑。

2.驱动端的上升和下降时间都为1ns。

3.传输线上每隔1 inch连接1个芯片负载。

4.传输线上的单位寄生电容为3pf/inch.每个芯片的等效电容为6pf。

5.传输线为带状线.介电常数为4.5,Z0=60欧姆.

问题:

(1) 传输线不在不接入负载的情况下的等效电容C/为多少?它的等效电感呢?

(2) 传输线接入负载后的等效阻抗为Z/ 为多少?

(3) 传输线在接入负载和未接入负载情况下分别的传输速度是多少?(ps/inch)

这么深奥,路过的!

··不是面试的笔试题吧。看着牙酸

不是,学校里面的研究生考试题,大家可以拿出来晒晒,看能答对几个

这种题目没有太大的实际意义!

第三个问题我比较好奇,有无负载会影响信号的速度么?

求解答

信号传输速度只和周围的介质有关,和负载无关,这是我们的理解!

PCB 上的信号线在无负载情况下的传输速度只与介质材料的介电常数相关,在包含负载的情况下,使得传输线上电容发生变化,传输延时变大,速度变小,以上理解不知道对不

以Tr/6作为传输线的分段依据,本问题Tr=1ns,换算后每1inch可以用集总RLGC模型参数建模:

(1) 传输线不在不接入负载的情况下的等效电容C/为多少?它的等效电感呢?

单位电感为:由(L/C)^(1/2) = 60Ω,可知L = 10.8nH/inch

等效总电容为:8*3pF/inch = 24pF

等效总电感为:8*10.8nH/inch = 86.4nH

(2) 传输线接入负载后的等效阻抗为Z/ 为多少?

Z = (L/C1)^(1/2) ,其中C1 = 3+6 =9pF/inch,故Z = 10.95Ω

(3) 传输线在接入负载和未接入负载情况下分别的传输速度是多少?(ps/inch)

不接入负载时:Td = (L*C)^(1/2) = 180ps/inch

接入负载时:Td = (L*C1)^(1/2) = 311.8ps/inch