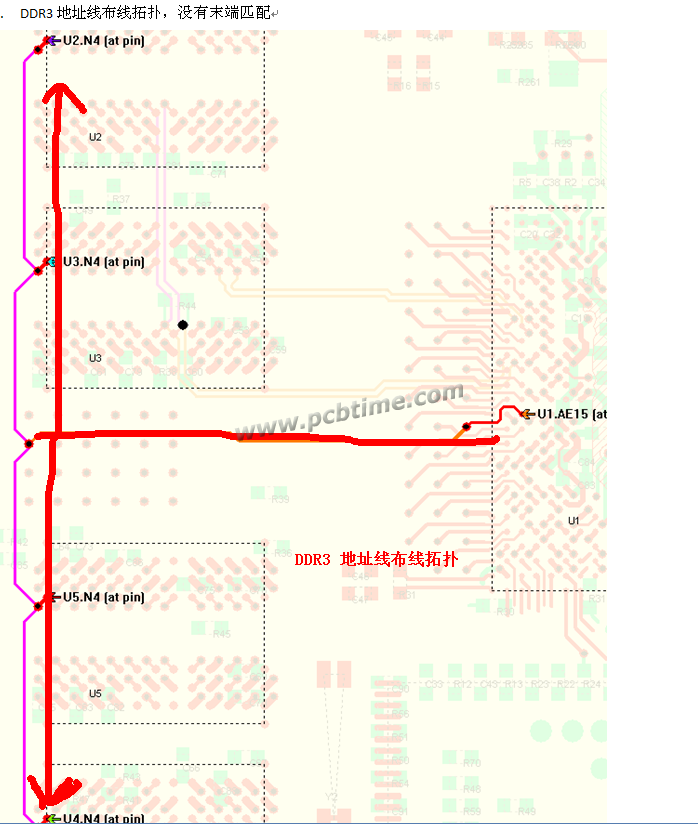

DDR3 地址线拓扑的可行性

时间:10-02

整理:3721RD

点击:

DDR3 地址线拓扑的可行性,各位发表一下看法,谢谢

优缺点, 可行性

自己定一个

当然是可行的,取决于你的驱动强弱或者是否可调。最好的办法是通过仿真就可以知道具体是否可行了。

波形还可以,下冲超标

时钟线仿真出来的,cross电压不在0.75V的误差范围,而且左右的交叉电电压一个高于0.75很多,一个低于0.75很多

你不是问的地址信号吗,怎么又跑到时钟信号上面去了呢?时钟信号还是要端接的好!

地址也问,时钟也问哈,这个时钟的短接是一个末端跨接的电阻 还是150欧姆的,是加上短接仿真出来的结果

前面看错了,以为是纯粹的T型拓扑,这种拓扑还是有一定风险的,T型加菊花链的拓扑,很少这样做的,要不然就正反贴,要不然就后面一级分支再等长。

以前的DDR2这样做过也对,DDR3人家说以前都是这样做的800MHZ是没问题,哎,难以琢磨

别太纠结