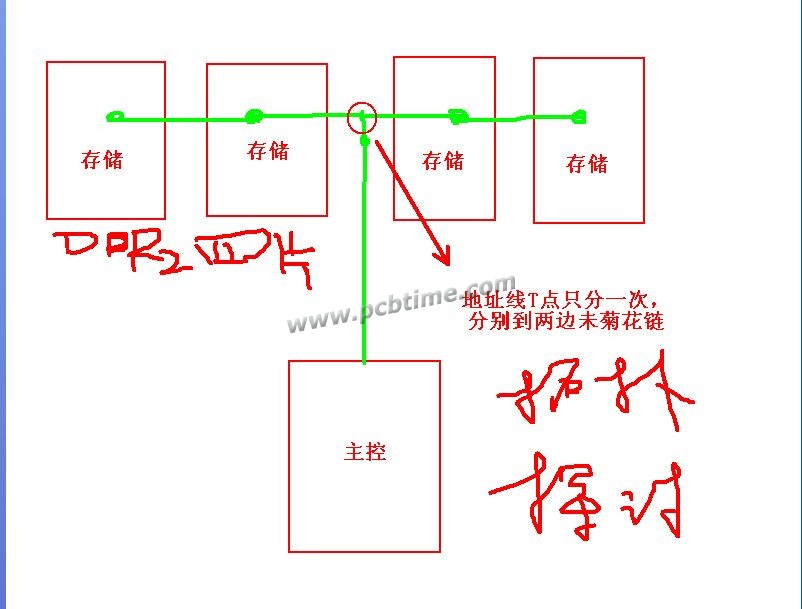

DRR2拓扑探讨,你怎么看?

时间:10-02

整理:3721RD

点击:

DRR2拓扑探讨,你怎么看?

地址线没有办法等长啊

两片之间的距离很短是可以走的,例如少于600mil。建议做个简易的仿真,很容易得到。

400MH没有问题

意思是我们的ddr2地址线可以接受400mil的误差?

速率,有成功的例子,以前板子很密,有考虑成本时,速率要求不是很高的,都是采用这种拓扑,调试OK

非常好的讨论!

这种通常在空间有限的时候还是可以走的,如果是正反贴的就用得更多了。

表底贴的颗粒共用一组数据线这种是什么类型的拓扑,采用分时复用吗?请指教一下。谢谢。

小编说的是地址线。

我觉得这个应该是扩容。就是在控制器端口不够用的时候。这样连接可以节约控制器的端口。这样可以通过片选的方式实现扩容。不知道哪位大神有没有其他认知。可以分享下。

楼上的说法没错,如果是数据组这样接的话就是扩容了,但一般也不会接4片,2片而已,这样的结构是不太能支持很高的数据率的。