差分时钟的问题

时间:10-02

整理:3721RD

点击:

高速先生,您好!

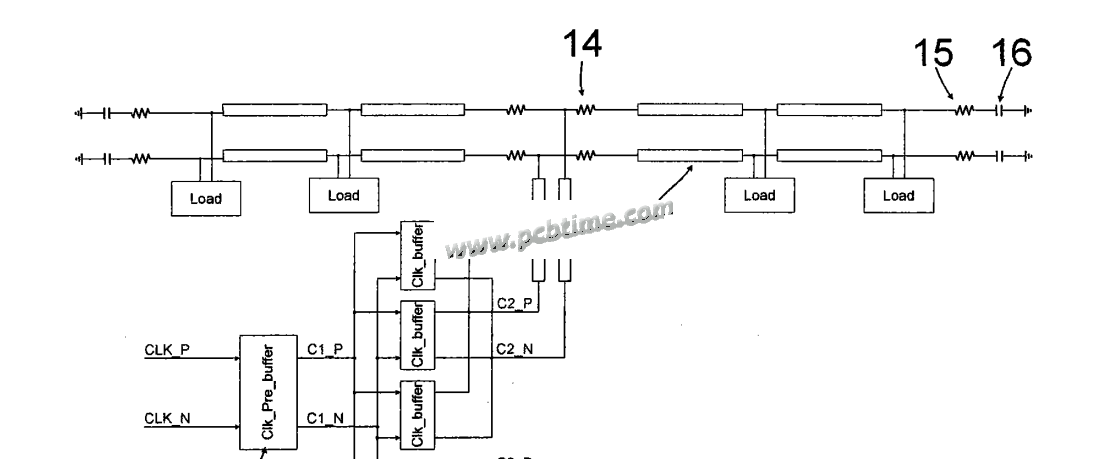

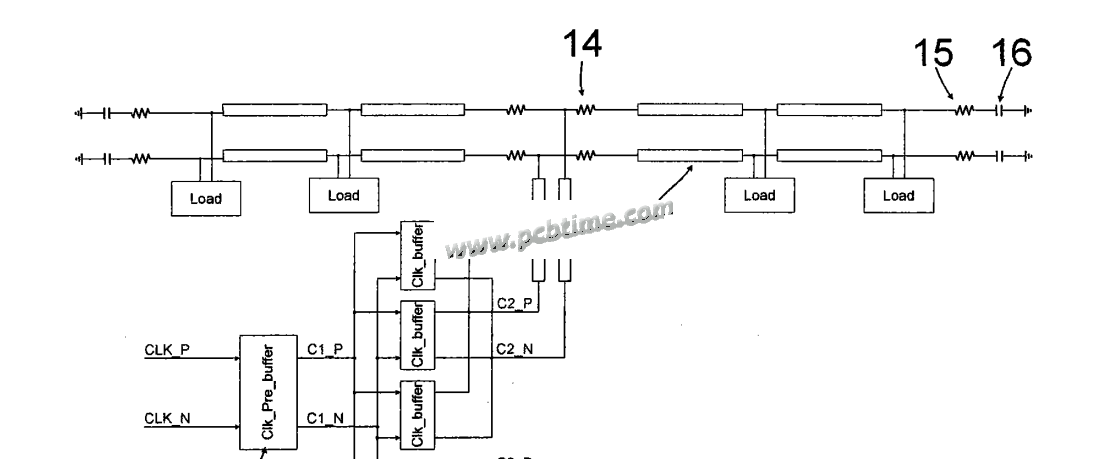

这是一个差分的时钟,我想问一下这里接14,15,16的原理是什么? 15,16就是并行AC端接吧,主要是我不明白接一个14的原理是什么? 感谢!

这是一个差分的时钟,我想问一下这里接14,15,16的原理是什么? 15,16就是并行AC端接吧,主要是我不明白接一个14的原理是什么? 感谢!

差分信号, 时钟

从图上看,你这个是远端簇型的拓扑,也可以说是T型结构,但这个T型前面的主干比较短,分支比较长,

所以在分支后面分别加串阻来匹配;反过来,如果T型前面的主干很长,分支很短(DDR2常规的T型走线),那这个串阻通常就放到T点前面的主干线上,分支上就不要加了。

14这个电阻的作用主要还是起端接匹配的。

这个你要看电阻阻值。

有可能是串阻,作为T点处消除反射的,在一些情况下有用,不建议这样加。

也有可能是选焊的电阻,可以将一边开路。

小编好厉害!看看

我看有介绍拓扑结构相关的书籍没有看到有关这种分支加串阻的匹配啊,请推荐个有关知识的书籍或者网站吧。

恩,小编有没有好推荐的呢

这些东西跟信号完整性相关,弄明白反射了就明白这些地方是怎样了。推荐看完告诉先生反射系列。觉得那些地方还不太明白的话描述一下,高速先生可以为此再写一篇文章。