DDR3地址线差分时钟差模电压数值是多少?

时间:10-02

整理:3721RD

点击:

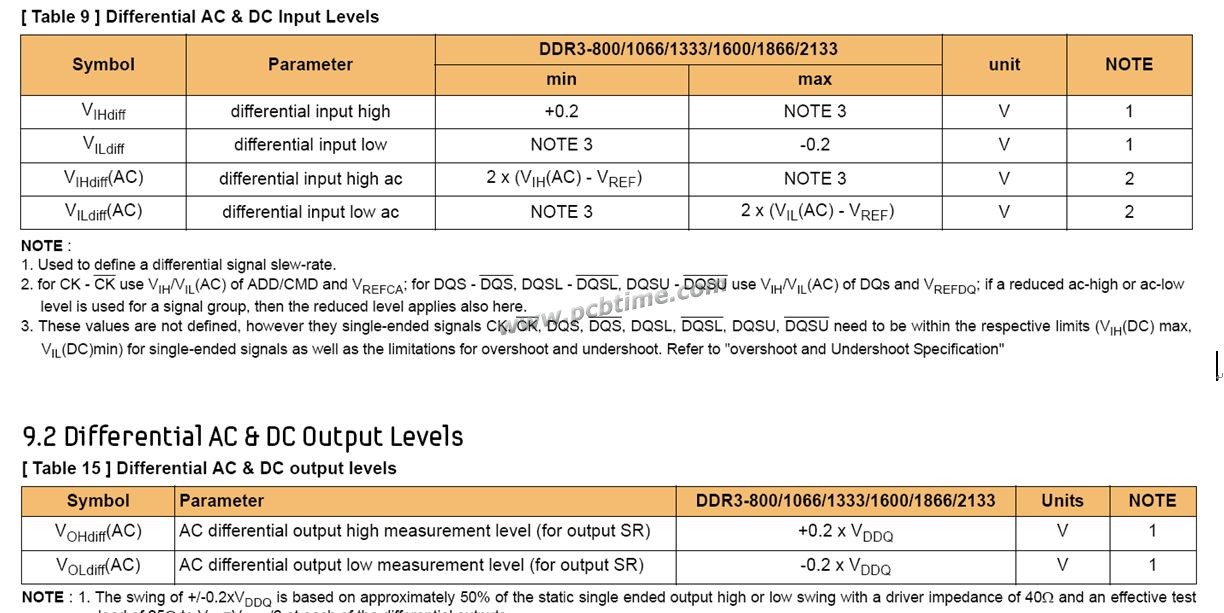

求助一下,对于DDR3地址线差分时钟差模电压的peak to peak的数值范围是多少?谢谢,从下面的参数中哪里可以得出

路过,帮顶

地址线?差模?老兄,应该是时钟信号吧。这个表里面只有Vih和Vil,Vdiff一般没有要求,但一般也不会太高的,正常应该在-Vdd到+Vdd以内,这个没有太多要求的。

就是时钟信号,差模 共模都没有要求吗?那对已一般的差分如果差模和共模的数值大于要求,对信号的影响体现在那些方面,求答

Vdiff=(V+)-(V-);Vcomm=(V+)+(V-),Vdiff和Vcomm超标一般体现在形成他们的单端信号不均衡,Vdiff是关于0电平对称,Vcomm是在单端电平的一半处,Vcomm如果超标,那Vcross(即单端交叉点处)也会超标,说明两根单端信号严重不对称,造成的原因可能是差分线的等长不一致(die到die),芯片(模型)内部的偏移等。影响就是对信号的判断及造成共模干扰。

大牛一枚,鉴定完毕,嘿嘿,谢谢专业的解答

那也就是意味着,仿真出来的参数,peak to peak 的数值就是差模电压,对吗?感谢

非常好的讨论,顶起