理性认识SQ的时序仿真功能(转载)

时间:10-02

整理:3721RD

点击:

SQ所谓的时序仿真功能事实上是在一个测量和套用公式的过程。

(会用软件不代表什么,理解软件的工作原理才是正道----软件中计算的理论基础)

(顺便提一下,利用Hyperlynx你一样可以实现时序计算,只是更多的工作量要自己去做)

测量:

1.实时的buffer驱动能力设置(slow,typical or strong)

2.flight time的选择(max or min)

3.AC test condition的确定

4.修改模型,确保model的正确性

5.注意同时考虑rise and fall edge0

6.skew及jitter的考虑)

***********************************************

先从时序分析的一些概念入手。

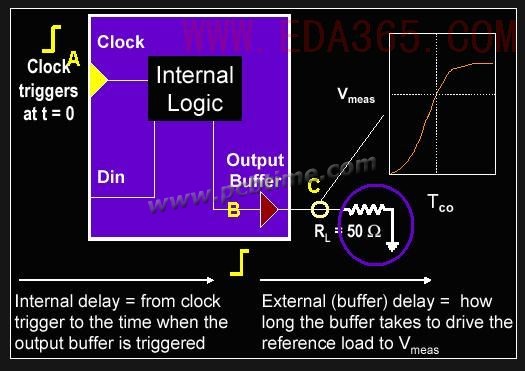

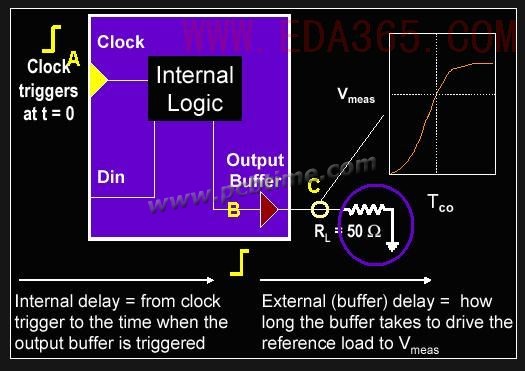

tco

----clock to output delay

指时钟触发开始到有效数据输出的器件内部所有延时的总和。Tco 包含缓冲延时buffer delay和逻辑延时logic delay。

这是个及其重要然而又被许多人错误理解的问题。

logic delay

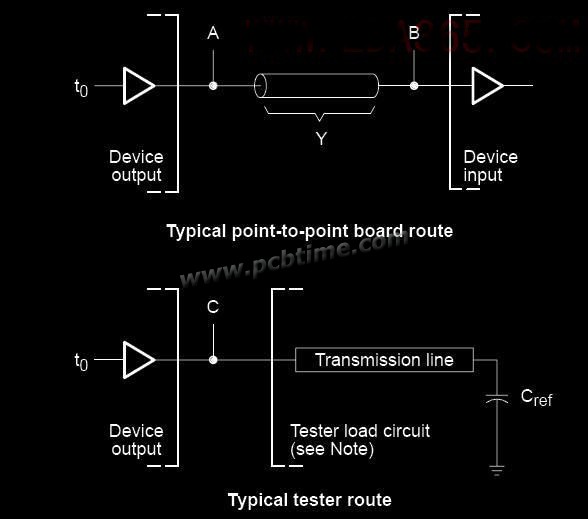

A、B点间的delay就是logic delay,从输入端(A点)的时钟触发到输出缓冲器(B)触发的时间间隔。

logic delay是由IC本身决定的,其延时信息厂家是以SDF(static delay file)文件提供的,在design的那一刻就被工艺参数和电气所决定

buffer delay

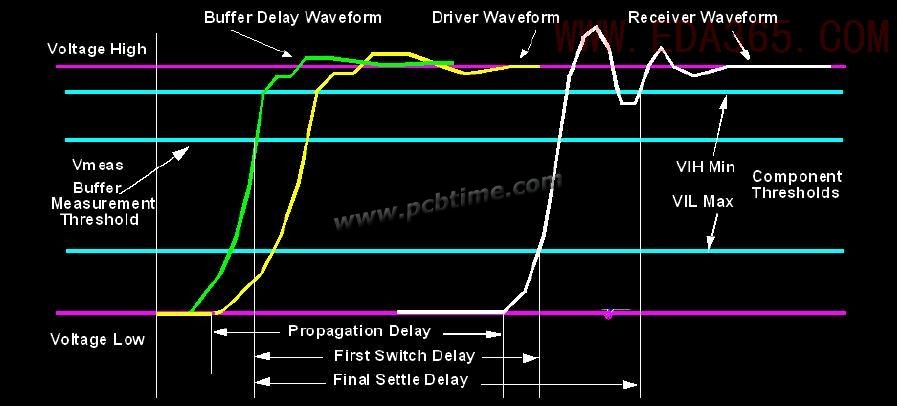

B、C点间的delay是buffer delay,是指信号经过缓冲器达到有效的电压输出所需要的时间,从下图看即为从B点buffer开关的时间t=0点开始,到C点电压达到Vmeas的时间。

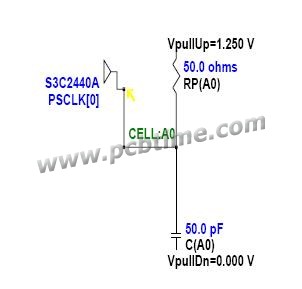

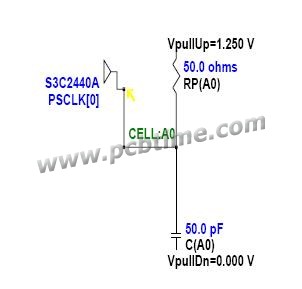

buffer delay是和load情况密切相关的,这里看到的是一个50ohm的测试负载,这仅仅是一个例子,不同的芯片其测试条件一般是不同的

许多人误认为Tco就是buffer delay,这种理解是极其错误的。

1.负载特性决定了buffer delay的不同(variant due to different load)

2.IC design决定了logic delay的确定(constant)

由tco = logic delay + buffer delay 可得,Tco的数值也会随着load情况而变化

可我们在datasheet中的tco又是如何得来的呢,这就要讲到AC test condtion的问题,进而讲到修正,Vmeas等等

****************************************

Vmeas and test load descirption

Vmeas and test load descirption

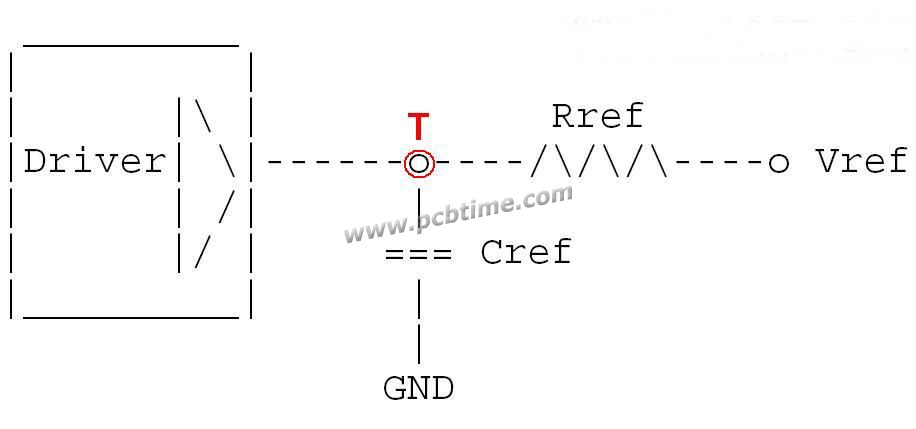

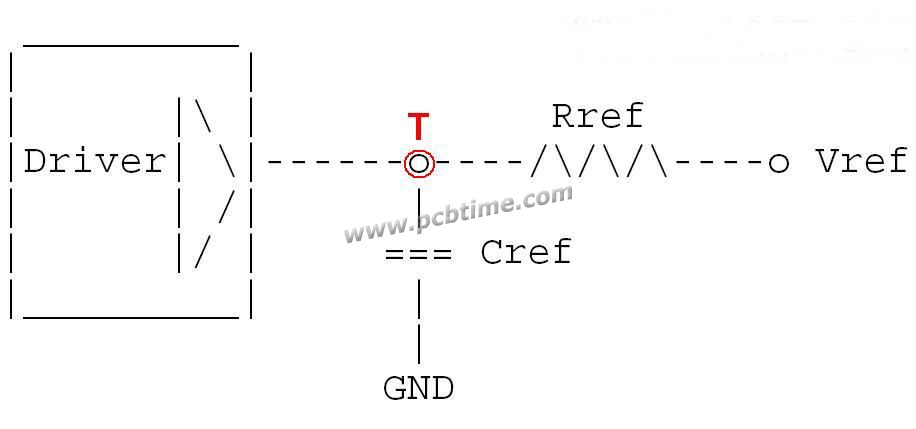

前面已经讲过Tco概念,那么手册中的Tco是如何得到的呢?

请看下图,半导体厂商首先会根据芯片特性确定具体的test load(不要深究为什么如此,如果想清楚理解,意味着你要进入一个新的领域----IC测试),我们的probe点即为T点,Tco的定义即为从时钟输入到数据输出的时间,而数据输出的时间点的确定即为T点波形上升为Vmeas的时间点。

Vmeas为半导体厂商用来为输出buffer(当然包含output ,I/O,3-state)确定板级延时特性的电压参考点

Vref,Rref,Cref为半导体厂商用来指明传输延时和输出buffer开关特性的test load

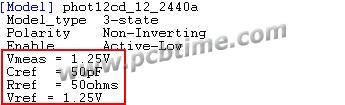

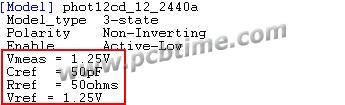

举个例子

这是取自一个ibis model clk buffer的test laod及Vmeas参数

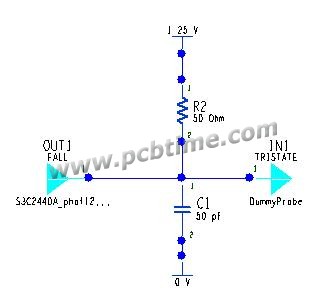

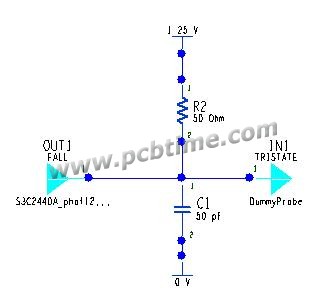

下面分别用SQ和hyperlynx搭建起test load

SQ

hyperlynx8

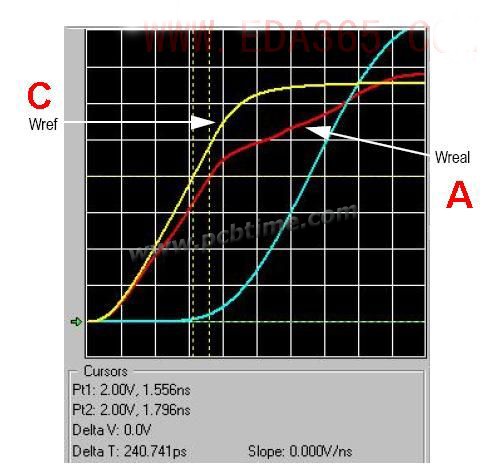

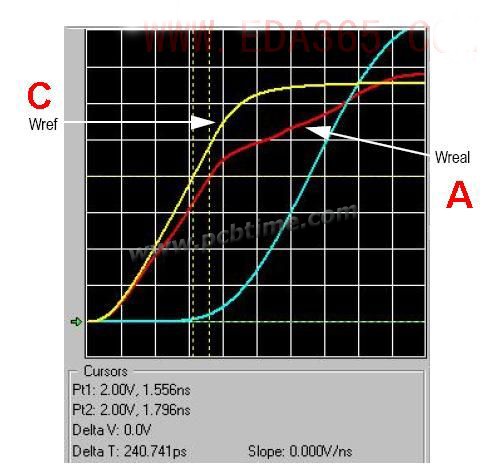

C点波形即为test load情况下的驱动端波形

A点波形即为actual load 情况下的驱动端波形

B点波形即为actual load 情况下的接收端波形

我们将A,C间的时间间隔(电压参考点为Vmeas)即为我们的补偿时间compensation timing-----------Tcom

这里的Tcom为240.741ps

而A,B间的时间间隔即为我们的板上走线延时(注意,这里的板上延时不同于传输延时)---------------Tlayout

Tlayout是我自己定义的,见笑啊(要说明的一点是,这里只是为了说明问题,定义不合适的还请海涵)

板上走线延时的电压参考点依据信号的类型有所不同

1.对于时钟信号来说,参考电压点为Vmeas,因为时钟信号要求严格的单调性(我们这里研究的是同步系统,参考信号为CLK)

2.对于控制信号,地址信号,数据信号来说,起始参考点为驱动端Vmeas,终了参考点为接收端Vil/Vih(非CLK信号不要求有很好的单调性,故引入门限电平作为参考点,避免非线性边沿造成的巨大误差)

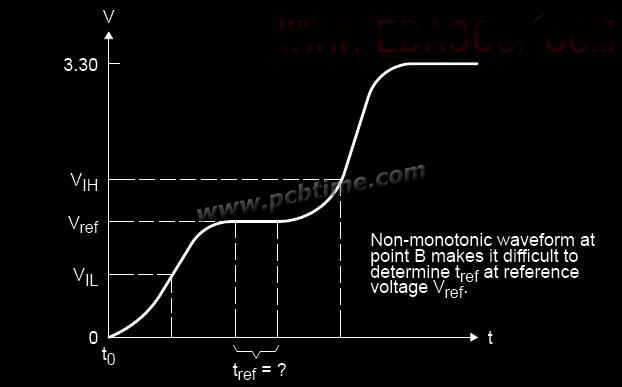

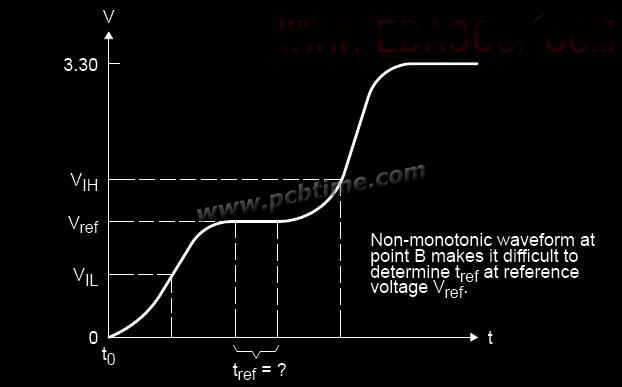

就像下图,Vmeas电平持续Tref时间,非线性边沿的存在使得我们不能将Vmeas作为参考。

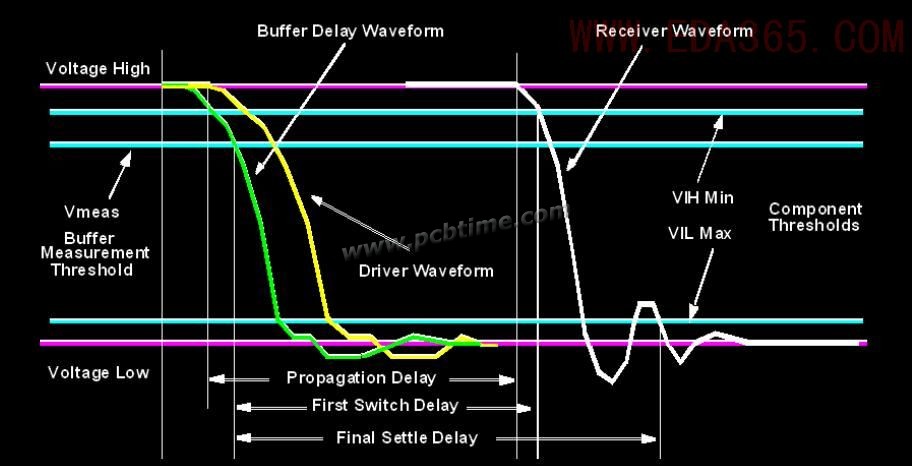

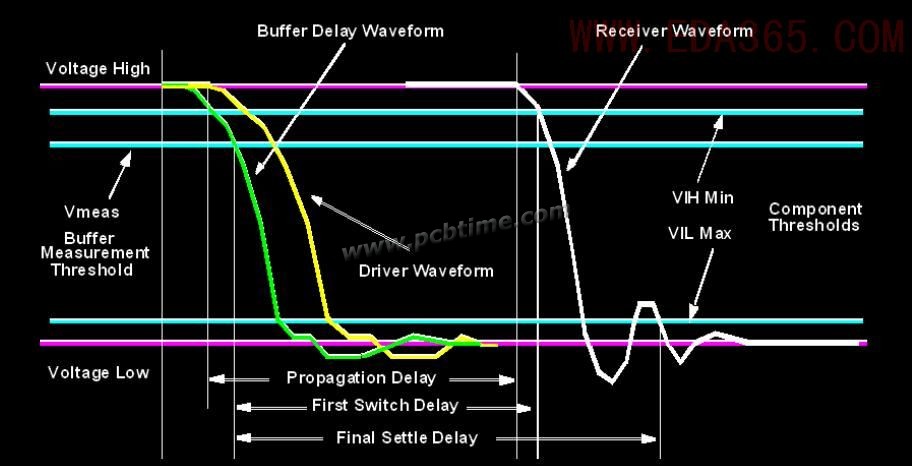

settle delay-----建立延时,对于上升沿,就是Vih作为参考电压点,对于下降沿,就是Vil作为电压参考点

对于单独的上升沿下降沿来说,开启延时定义为first switch delay,建立延时定义为final settle delay

上升沿和下降沿中两个first switch delay最小值即为switch delay。

上升沿和下降沿中两个final settle delay最大值即为settle delay。

(至于为什么取最小和最大,到了后面的实际时序计算过程就明白了)

(会用软件不代表什么,理解软件的工作原理才是正道----软件中计算的理论基础)

(顺便提一下,利用Hyperlynx你一样可以实现时序计算,只是更多的工作量要自己去做)

测量:

1.实时的buffer驱动能力设置(slow,typical or strong)

2.flight time的选择(max or min)

3.AC test condition的确定

4.修改模型,确保model的正确性

5.注意同时考虑rise and fall edge0

6.skew及jitter的考虑)

***********************************************

先从时序分析的一些概念入手。

tco

----clock to output delay

指时钟触发开始到有效数据输出的器件内部所有延时的总和。Tco 包含缓冲延时buffer delay和逻辑延时logic delay。

这是个及其重要然而又被许多人错误理解的问题。

logic delay

A、B点间的delay就是logic delay,从输入端(A点)的时钟触发到输出缓冲器(B)触发的时间间隔。

logic delay是由IC本身决定的,其延时信息厂家是以SDF(static delay file)文件提供的,在design的那一刻就被工艺参数和电气所决定

buffer delay

B、C点间的delay是buffer delay,是指信号经过缓冲器达到有效的电压输出所需要的时间,从下图看即为从B点buffer开关的时间t=0点开始,到C点电压达到Vmeas的时间。

buffer delay是和load情况密切相关的,这里看到的是一个50ohm的测试负载,这仅仅是一个例子,不同的芯片其测试条件一般是不同的

许多人误认为Tco就是buffer delay,这种理解是极其错误的。

1.负载特性决定了buffer delay的不同(variant due to different load)

2.IC design决定了logic delay的确定(constant)

由tco = logic delay + buffer delay 可得,Tco的数值也会随着load情况而变化

可我们在datasheet中的tco又是如何得来的呢,这就要讲到AC test condtion的问题,进而讲到修正,Vmeas等等

****************************************

Vmeas and test load descirption

Vmeas and test load descirption

前面已经讲过Tco概念,那么手册中的Tco是如何得到的呢?

请看下图,半导体厂商首先会根据芯片特性确定具体的test load(不要深究为什么如此,如果想清楚理解,意味着你要进入一个新的领域----IC测试),我们的probe点即为T点,Tco的定义即为从时钟输入到数据输出的时间,而数据输出的时间点的确定即为T点波形上升为Vmeas的时间点。

Vmeas为半导体厂商用来为输出buffer(当然包含output ,I/O,3-state)确定板级延时特性的电压参考点

Vref,Rref,Cref为半导体厂商用来指明传输延时和输出buffer开关特性的test load

举个例子

这是取自一个ibis model clk buffer的test laod及Vmeas参数

下面分别用SQ和hyperlynx搭建起test load

SQ

hyperlynx8

聊过了buffer delay,同时也明白了buffer delay会随着load情况的变化而变化。

而我们实际关心的应该是test load情况下的buffer delay,他将作为我们时序分析的参考基准,其重要性可想而知。

Tco的提出是基于test load的测试结果,buffer delay作为tco的组成部分直接影响Tco,很显然,我们实际系统系统的load情形是不同于test load的。那么就要考虑到如何修正Tco的问题。

借用TI的图说明一下。

C点波形即为test load情况下的驱动端波形

A点波形即为actual load 情况下的驱动端波形

B点波形即为actual load 情况下的接收端波形

我们将A,C间的时间间隔(电压参考点为Vmeas)即为我们的补偿时间compensation timing-----------Tcom

这里的Tcom为240.741ps

而A,B间的时间间隔即为我们的板上走线延时(注意,这里的板上延时不同于传输延时)---------------Tlayout

Tlayout是我自己定义的,见笑啊(要说明的一点是,这里只是为了说明问题,定义不合适的还请海涵)

板上走线延时的电压参考点依据信号的类型有所不同

1.对于时钟信号来说,参考电压点为Vmeas,因为时钟信号要求严格的单调性(我们这里研究的是同步系统,参考信号为CLK)

2.对于控制信号,地址信号,数据信号来说,起始参考点为驱动端Vmeas,终了参考点为接收端Vil/Vih(非CLK信号不要求有很好的单调性,故引入门限电平作为参考点,避免非线性边沿造成的巨大误差)

就像下图,Vmeas电平持续Tref时间,非线性边沿的存在使得我们不能将Vmeas作为参考。

上次聊过,Tcom(补偿时间)+Tlayout(板上走线延时)=flight time(飞行时间有min、max之分,之所以如此划分是因为我们的电压参考点为Vil/vih)

对于时钟线是没有min和max飞行时间之分的。而地址线,数据线,控制线等才会牵涉到min,max(时钟信号要求严格的单调性,故可以用Vmeas作为参考电压点,而其他信号线不要求严格单调性,故要以Vil/vih作为电压参考点).

min/max flight time,SQ定义为switch delay和settle delay(这里不得不把candence赞一下,这个定义很形象)

switch delay----开启延时,对于上升沿,就是Vil作为参考电压点,对于下降沿,就是Vih作为电压参考点

settle delay-----建立延时,对于上升沿,就是Vih作为参考电压点,对于下降沿,就是Vil作为电压参考点

对于单独的上升沿下降沿来说,开启延时定义为first switch delay,建立延时定义为final settle delay

上升沿和下降沿中两个first switch delay最小值即为switch delay。

上升沿和下降沿中两个final settle delay最大值即为settle delay。

(至于为什么取最小和最大,到了后面的实际时序计算过程就明白了)

这个很详细,需要好好鼓励下!

好资料,顶了

嘿嘿

顶一下!

互相学习