10G以上的信号可以走表层吗?有什么影响

时间:10-02

整理:3721RD

点击:

除了EMI影响,从SI的角度,10G以上的信号可以走表层吗?有什么影

表层传输速率快些,也可以减少过孔的影响

表层的阻抗和时延不好控一点,如绕线等长的话没有带状线好控制。

除了这些其实还是有10G信号走表层的,也有成功例子,并不是一棍子打死,

SI里面很经典的一句话,权衡的艺术。

一般走表层就是想忽略过孔的影响,还有就是不用打背钻,不过如果一定要走表层,尽量走直线少去拐角绕线等,否则差分线的正负时延很容易就不一致的。

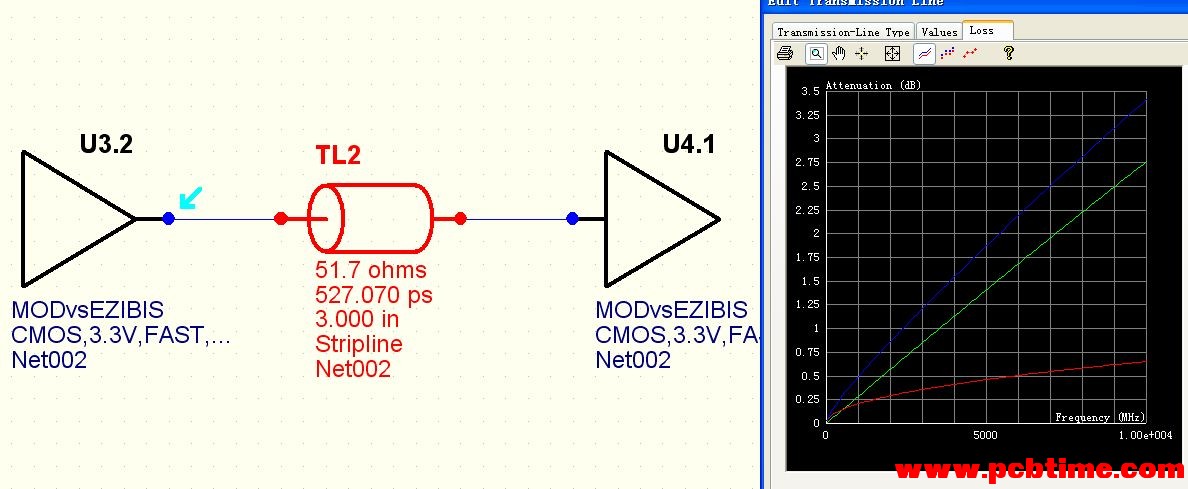

微带线的窜扰大于带状线,其次微带线的损耗也是大于带状线,微带线延迟较小,速度较快,阻抗不易控制,走线的能量辐射和EMI可能会超标,这个还的综合考虑,嘿嘿

微带线损耗大于带状线?有什么依据吗?或者说有什么约束条件吗?

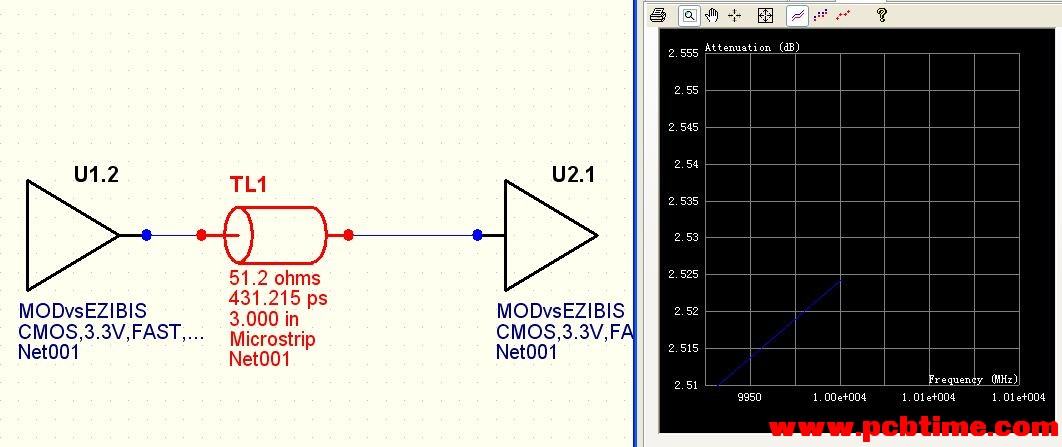

反了,具体看图

像这些SERDES能走表层有很多好处,我经常把XFI,SFI那些信号表底层走

哈哈,范范真是仔细。