DDR信号线阻抗疑问?

时间:10-02

整理:3721RD

点击:

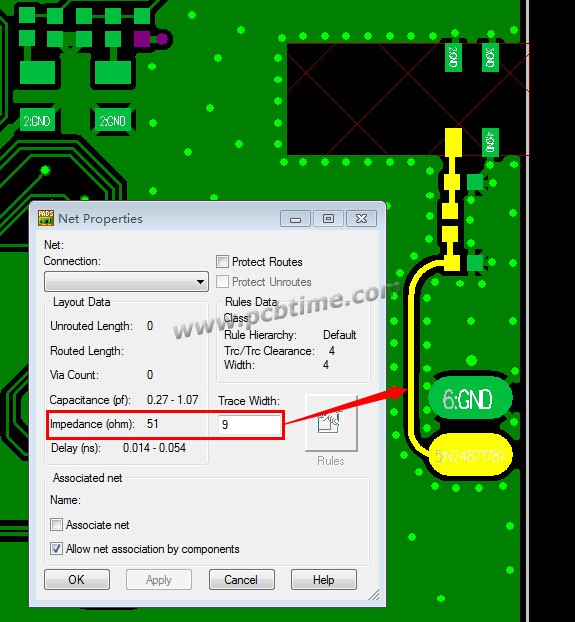

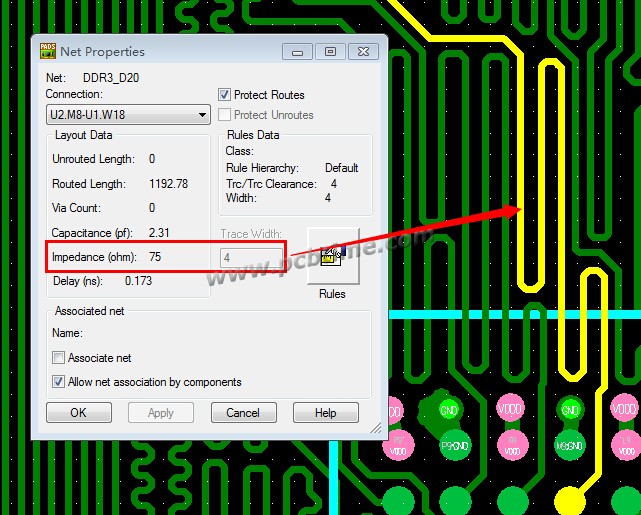

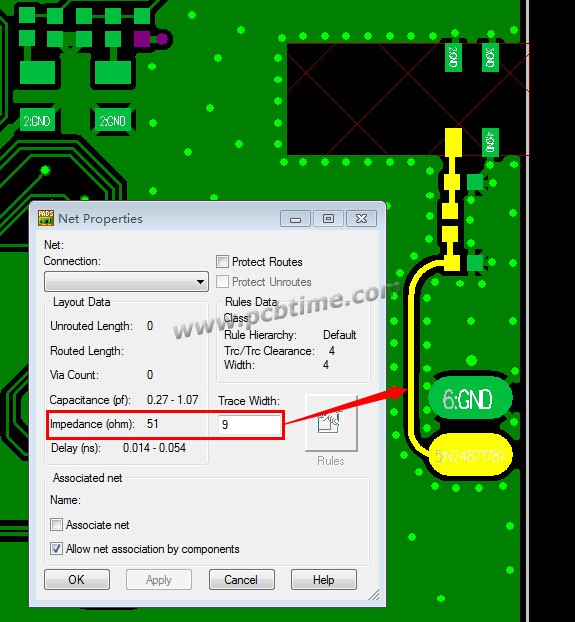

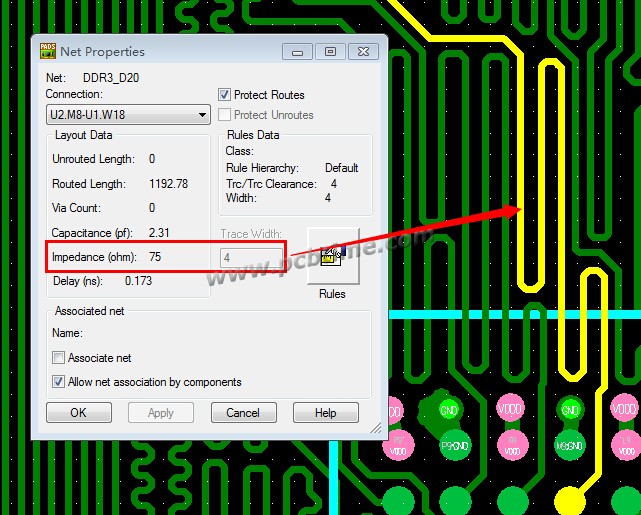

在一块PCB板上,有RF、DDR电路,一般我们都要对RF天线信号、DDR的数据线、地址线做50欧姆的阻抗控制,天线的走线线宽我看到大部分的PCB都设置8mil—12mil左右,而DDR部分由于元件引脚分布密度较高只能走4mil-5mil,那么在满足天线信号等于50欧姆的情况下,DDR信号肯定会比50欧姆大很多,大概在75欧姆左右,这是不是一个问题?

DDR, 阻抗

阻抗不止跟线宽由关系,还跟介质,距离平面的距离等有关系。

比如,数据线参考第二层,走5mil。

RF线下方第二层掏空,参考第三层,走12mil。他们可以同时都是50欧姆的

这种情况,如果是射频,一般会做隔层参考。天线应该也可以吧

DDR是几代的,如果是DDR2,走线又不太长的话,可以这么做。如果是DDR3,阻抗这么高,是不可以的,天线可以使用隔层参考来提高阻抗。

通常都是挖空相邻层,隔层参考。

楼上的观点都是可以的。

四层板,由于PCB较厚1.6mm,2、3层离得远,这样第1层很难参考到第3层

原来如此,DDR2勉强可以。

不过公司领导指示:天线走4.1mil线宽!个人感觉是不是太细了

谢谢大家.隔层参考确实是一种办法,但这板子太厚了,老大最后决定天线信号线走4.1mil线宽。

这种情况,如果是射频,一般会做隔层参考。