Error带来的人生思考——设计先生之回流设计系列(1)

时间:10-02

整理:3721RD

点击:

本文作者:杨洲 设计先生团队队员

有不少朋友反映Mr.S写的理论太枯燥太难看了,Mr.S已经躲角落哭去了,现在轮到我MR.Lay登场。

我们先看电子场的两个事实:

1,电流是电荷的流动;

2,电流只能在闭合的回路中流动;

接着我们先理解下什么是信号回流路径,低速和高速返回路径是否一致:

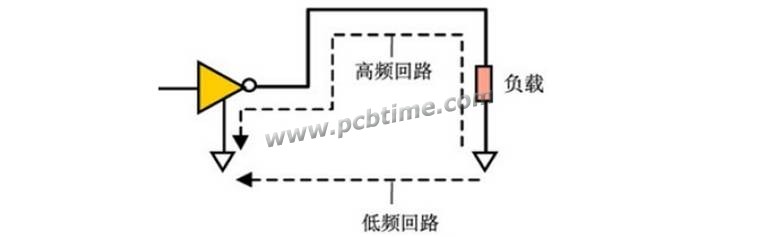

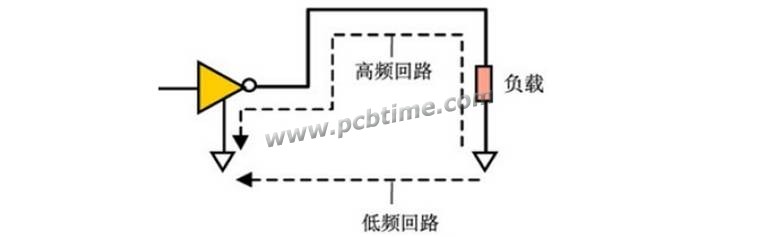

信号回流路径,即return current。信号流向是从驱动器沿PCB传输线到负载,再由负载沿着地或电源通过最短路径返回驱动器端。这个在地或电源上的返回信号就称信号回流路径。

每一个信号都有一个回流路径来构成回路。那么作为设计者就必须考虑并控制它在电路板上的位置。

低速电路中,电流沿着最小电阻路径前进。低速电流从驱动端传输到负载端,然后沿着地平面返回到驱动端。返回电流沿着最小电阻的路径,它返回的电流密度和该路径上的电导相对应。

高速电路中,对于一个特定的电流返回路径,电感要远比其电阻重要。高速的返回电流沿着电感最小路径前进,而不是电阻最小路径。电感最小的返回路径就紧贴在一个信号导体下面,它使输出电流路径和返回电流路径之间的总面积最小。返回信号的电流密度随着其相互距离增加的平方而下降。

当知道理论了以后,接着就是理解它并记住它。

设计先生深刻的明白什么会给我们印象最深,那就是error带来的教训。小时候你会记得老师的表扬,但更能记得你放错误后老师的嘲笑或者那一种眼神。因为这是我们成长过程中必然会遇到的。设计先生觉得与其在天堂里受到无所谓的知识灌输还不如在地狱里艰难磨练的自我成长。打击才是前进的动力。

我们从下面这个打击开始进入主题。

时钟线振铃的产生

案例描述:

十层板,CLK走在第四层(信号层),第五层是完整的电源平面,第三层也是信号层,但与第四层相差较远,第二层是地层。当我们只打开第四层时,发现时钟布线没有什么问题。当打开第四层第五层,发现差分过孔在平面层反盘做得很大,在电源层比其他过孔避让要多很多。于是就发现时钟在电源层差分过孔旁边跨了很多次分割。

案例原因:

信号CLK以相邻的第五层电源层为参考平面,构成回流路径时,由于反焊盘的存在使该路径增长,造成很多处回流路径阻抗的不连续。从而对信号构成了影响。

案例解决:

将第四层的时钟信号线换到了第三层,且避开了平面层差分过孔反盘很大的区域,从而保证了参考的地平面,同时回流也是完整的。改善后时钟线振铃消失。

案例启示:

1, 重点检查回流路径是否完整。

2, 相邻层之间是否存在高速信号的长距离平行走线。

这个PCB设计上的案例为什么会带来人生的思考?其实回流路径就像是回家的路,我们记得出来打拼,但往往却忘记了我们还要回去,外面的世界很漂亮,也很繁华,一方面吸引着我们,另外一方面也迷失着我们,于是我们会开始渐渐忘了我们的初心。来时的路我们都会记得,可是回去的呢?偶尔记得要回去看看,就像上面的案例,可是我们总被各种忙,各种聚会,各种所谓的梦想围绕着,结果就导致我们回不去了。

无论是设计还是生活,要记得我们的源,出来了还要记得回去的路。

Question: 对双层板的DDR设计有哪些注意点?

有不少朋友反映Mr.S写的理论太枯燥太难看了,Mr.S已经躲角落哭去了,现在轮到我MR.Lay登场。

我们先看电子场的两个事实:

1,电流是电荷的流动;

2,电流只能在闭合的回路中流动;

接着我们先理解下什么是信号回流路径,低速和高速返回路径是否一致:

信号回流路径,即return current。信号流向是从驱动器沿PCB传输线到负载,再由负载沿着地或电源通过最短路径返回驱动器端。这个在地或电源上的返回信号就称信号回流路径。

每一个信号都有一个回流路径来构成回路。那么作为设计者就必须考虑并控制它在电路板上的位置。

低速电路中,电流沿着最小电阻路径前进。低速电流从驱动端传输到负载端,然后沿着地平面返回到驱动端。返回电流沿着最小电阻的路径,它返回的电流密度和该路径上的电导相对应。

高速电路中,对于一个特定的电流返回路径,电感要远比其电阻重要。高速的返回电流沿着电感最小路径前进,而不是电阻最小路径。电感最小的返回路径就紧贴在一个信号导体下面,它使输出电流路径和返回电流路径之间的总面积最小。返回信号的电流密度随着其相互距离增加的平方而下降。

当知道理论了以后,接着就是理解它并记住它。

设计先生深刻的明白什么会给我们印象最深,那就是error带来的教训。小时候你会记得老师的表扬,但更能记得你放错误后老师的嘲笑或者那一种眼神。因为这是我们成长过程中必然会遇到的。设计先生觉得与其在天堂里受到无所谓的知识灌输还不如在地狱里艰难磨练的自我成长。打击才是前进的动力。

我们从下面这个打击开始进入主题。

时钟线振铃的产生

案例描述:

十层板,CLK走在第四层(信号层),第五层是完整的电源平面,第三层也是信号层,但与第四层相差较远,第二层是地层。当我们只打开第四层时,发现时钟布线没有什么问题。当打开第四层第五层,发现差分过孔在平面层反盘做得很大,在电源层比其他过孔避让要多很多。于是就发现时钟在电源层差分过孔旁边跨了很多次分割。

案例原因:

信号CLK以相邻的第五层电源层为参考平面,构成回流路径时,由于反焊盘的存在使该路径增长,造成很多处回流路径阻抗的不连续。从而对信号构成了影响。

案例解决:

将第四层的时钟信号线换到了第三层,且避开了平面层差分过孔反盘很大的区域,从而保证了参考的地平面,同时回流也是完整的。改善后时钟线振铃消失。

案例启示:

1, 重点检查回流路径是否完整。

2, 相邻层之间是否存在高速信号的长距离平行走线。

这个PCB设计上的案例为什么会带来人生的思考?其实回流路径就像是回家的路,我们记得出来打拼,但往往却忘记了我们还要回去,外面的世界很漂亮,也很繁华,一方面吸引着我们,另外一方面也迷失着我们,于是我们会开始渐渐忘了我们的初心。来时的路我们都会记得,可是回去的呢?偶尔记得要回去看看,就像上面的案例,可是我们总被各种忙,各种聚会,各种所谓的梦想围绕着,结果就导致我们回不去了。

无论是设计还是生活,要记得我们的源,出来了还要记得回去的路。

Question: 对双层板的DDR设计有哪些注意点?

有一点不是很明白。小编讲到:信号回流路径,即return current。信号流向是从驱动器沿PCB传输线到负载,再由负载沿着地或电源通过最短路径返回驱动器端。这个在地或电源上的返回信号就称信号回流路径。给人的感觉是电流像水流一样,由发射端出发,经过信号路径到接收端,再从接收端由返回路径回到发送端。那么信号刚开始传输时,回流路径上就没有电流吗?答案是否定的,一开始返回路径上就是有电流的。信号线与参考平片(回流路径)构成传输线,回流路径不完整导致传输线阻抗不连续,因而信号出现反射,导致振铃,不知道我这样的解释合理吗?

为什么高速的时候,返回电流会集中在信号线下方。低速的时候,返回电流会寻找电阻最小的路径?很多资料上都是这么介绍的,但又很少说明为什么会这样。迫切希望小编能够多多指教,感谢!

什么是电阻最小路径?按照传输线理论,参考路径离信号路径越远,阻抗会越大。为什么电流集中在信号线下方,回路电感就小?低速的时候信号是怎么传输的呀,难道不是像分析传输线的二阶模型那样,一步一步向前传输的吗,如果是,返回电流又为什么会离信号线那么远,感觉好多地方都想不通的。

有个感抗公式吧,大概是围成的面积S有关,所以在信号线下面似乎最小。