DDR3系列之时钟信号的差分电容,一般人我不告诉他!

不是在这里回复哈,是在微信回复的。

1、差分电容用来消除反射:反射的本质原因还是因为阻抗不匹配,所以为何不用跨接电阻进行阻抗匹配?在海思3716M的方案中就是采用跨接电阻或者采用戴维南并联电阻进行阻抗匹配减少反射的。2、此处的电容值应该是对付EMI的,当时钟频率很高,上升沿比较陡,容易引起EMI问题,采用合适的电容来调整上升沿陡度,减少EMI;3、滤除高频噪声的作用肯定是有的,但是从这个角度考虑应该放在终端靠近DDR,而不是靠近源端;4、至于消除共模噪声,对于共模噪声来讲,两根差分线是一样的,应该根绝不到改电容的存在。以上是我个人的看法,请高速先生参考给出意见,共同探讨。

你说的跨接电阻和戴维南并联这个是相对于末端的端接哈,而这个差分电容是用在源端的端接;另外谁说高频噪声一定要在终端滤除?不能在源端就滤除了?虽然说差分线设计是一样的,但能100%保证实际效果上是一样吗?有考虑过玻纤效应、拐角的差异和加工差异吗?

1、滤除高频噪声在源端进行,那么从传输路径到DDR终端的过程中耦合的高频噪声你能用源端的电容滤去?滤波不在终端附近,意义是不大的。2、源端短接差分电容,容抗值取为差分阻抗,那么从终端看进来差分阻抗还是差分对设计的值么?电容与差分阻抗组合的作用后阻抗是怎么考虑的?

怎么觉得intel的这个时钟拓扑有点不对,只是觉得,末端应该接到0.75V把,altera是拉到0.75V的,xilinx的是拉到了0.75V,真的不知道到底拉倒多少,求解

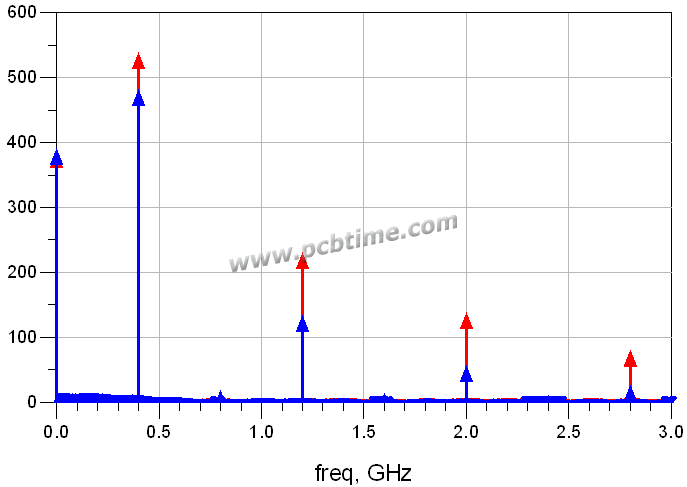

如图,红色为不接电容,蓝色为接电容,滤除的叫高频分量比较好,不要叫噪声。为何滤除高频分量可以让波形变好看,参考高速先生《反射系列》文章。至于阻抗匹配,可以不用考虑。

一般是啦到VTT,DDR3的话也就是0.75V,直接拉到地上的话会使得信号整体电平偏低。请仔细看intel的图,在电阻与地之间是有一个电容的。

这位兄台貌似会仿真,可以随便仿真一下就知道了。电容用100pf左右的。

时钟一般是通过电容到地或者Vcc,地址拉倒Vtt,这个是通用的做法,只是我们见到的拉到Vcc的多点。通过仿真可以看到波形其实没有太大的区别(印象中)。

是的,被前面的引导成高频噪声去了,其实应该是高频分量。关于ZXJ的第二个问题,作为端接,其实和末端的差分100欧姆电阻是一个道理,末端怎么考虑前端就怎么考虑,这个没必要太多纠结.

端接电阻的拉到地或者VCC的情况都有,多数为后者;出于功耗的考虑,拉到地势必会有额外的功耗增加,上拉到VCC比较合适;