“电源加磁珠”,想说爱你不容易(中)-PCB设计十大误区

作者:吴均 一博科技高速先生团队队长

温馨提示:记得看到最后,高速先生提一个问题,您可参与互动问答,回答有奖!

承前:从去耦半径出发,通过去耦半径的计算,让大家直观的看到我们常见的电容的“有效范围”问题。

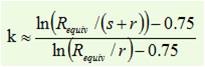

本节:讨论滤波电容的位置与PDN阻抗的关系,提出“全局电容”与“局部电容”的概念。能看到当电容呈现“全局特性”的时候,电容的位置其实没有想象中那么重要。

启后:多层板设计的时候,电容倾向于呈现“全局特性”,“电源加磁珠”的设计方法,会影响电容在全局范围内起作用。同时电源种类太多,还会带来其他设计问题。

通过上一篇文章,我们知道平常“耳熟能详”的电容去耦半径理论,对PCB设计其实没有什么指导意义。0.1uf的电容去耦半径足够大,设计中参考这个值没有用处,工程师还是会“尽量”把0.1uf电容靠近芯片的电源管教放置。PCB设计师需要更有效的理论来指导电容的布局设计。

既然简单的用四分之一波长理论推算的电容去耦半径不起作用,那么电容放置得离芯片电源管脚比较远,还会有哪些影响呢?很多人都答对了,影响安装电感。

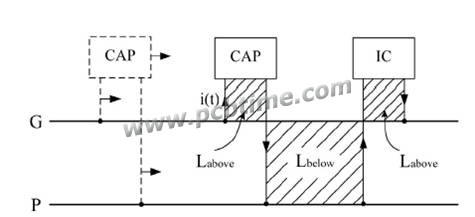

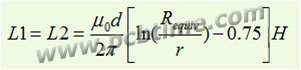

在上一个专题的第四篇文章里面,已经讨论过电容安装电感的估算。这一次,我们来更详细的看看安装电感。从图1能看到,安装电感可以简单分为L above和 L below。

图1

在这里引入两个概念:Labove 、Lbelow (电容和IC下面的电流回路大小不一定一样,但在这里分析的时候,假定大小等同)

总电感:LTotal= 2Labove+Lbelow

Labove包括电容的ESL和Fan out带来的电感,我们会另外专题讨论电容的Fan out问题。至于L below就更多收到电容位置的影响。简单来说,电容离芯片电源管脚越远,L below围成的面积就越大,相应的安装电感就越大。

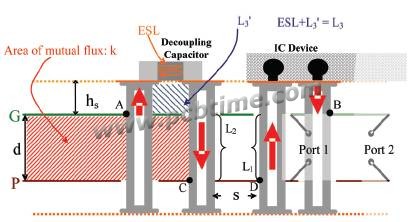

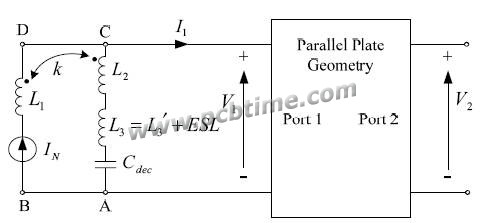

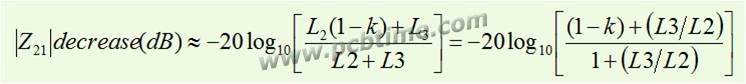

更具体点,Lbelow主要是两个过孔的自感和互感,当电容的位置离IC器件更近时,如图2所示,Lbelow的互感增大,因互感的作用与自感的作用相反,导致其整体电感减小,充放电速率更快

图2

可以列出一堆公式来推导这个互感乃至L below,但这个不是高速先生的风格。

其实从图1可以简单看出,G和P之间的距离对L below影响很大,G和P之间的距离越近,L below对应的阴影区域面积就越小。而L below越小,也就意味这电容可以放得越远,换句话说,电容的有效滤波范围更大。电容也就更加倾向于呈现“全局”特性。

下一节我们还会通过一个直观的仿真,让大家看到平面距离与安装电感的关系,以及为什么说在新的设计条件下,电容会呈现全局特性。

图3是一个简单的总结,更具体的分析,请听下回分解。

图3

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

磁珠是铁氧体材料制成,对高频能量衰减很大,利用这一作用来抑制电路中不必要的高频分量,磁珠的选择也是有讲究的,需要关注磁珠的参数指标等方面的选型应用要求,当电路需要纯洁直流供电时需要采用磁珠隔离高频能量,如单片机,音频电路,GPS,RF,运放电路等,磁珠也有分类使用的,用错了必然会导致电路出现异常,如:有些模拟地和数字地是不需要磁珠隔离的,使用了磁珠机会产生分地回路问题。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

滥用磁珠会增加成本,增加设计密度和难度,还会使芯片的电源响应变差;做的设计中一般比较敏感的小电流电源还有模拟电源会加磁珠隔离噪声;而一些高频的核电源加了磁珠反而不好。具体到电容滤波上会磁珠会使全局电容效果变差。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

加磁珠是为了隔离,减少模块间的窜扰,但是加磁珠又会把电源分的太散,容易导致信号线跨分割,同时占用太多空间

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

滥用磁珠会导致本来完整的平面被隔断,如有些资料会要求ddr的电源颗粒端与芯片端用磁珠隔开;只有两个系统会存在相互干扰的时候才用磁珠将电源隔开。比如模拟数字之间。加入磁珠会使电源的响应变差

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

1.磁珠会使电容离芯片管脚更远,使电容的作用变小,影响滤波效果;会给较密pcb布局带来一些困难。2.一些要求比较高的电路需要磁珠隔离,比如锁相环电路。3.磁珠会增加总的安装电感。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

1.磁珠会使电容离芯片管脚更远,使电容的作用变小,影响滤波效果;会给较密pcb布局带来一些困难。2.一些要求比较高的电路需要磁珠隔离,比如锁相环电路。3.磁珠会增加总的安装电感。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

电源加磁珠在低频电路中主要用作滤除电源的纹波,在高频电路中,受数字器件工作时电流大波动的影响,因为现在数字电路的电压在变小,而工作电流呈现大的增长,假定L不变,在L上会产生大的电压跃变V=Ldi/dt,反过来制约和影响电源的供电。给电路正常工作带来负面影响。

问题来了!

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?回复有奖。回复“奖品”查看问答奖品。

我的答案:

滥用磁珠会影响电容在全局范围起作用。磁珠的作用 :抑制信号线、电源线上的高频噪声和尖峰干扰,还具有吸收静电脉冲的能力。