带隙基准仿真的问题

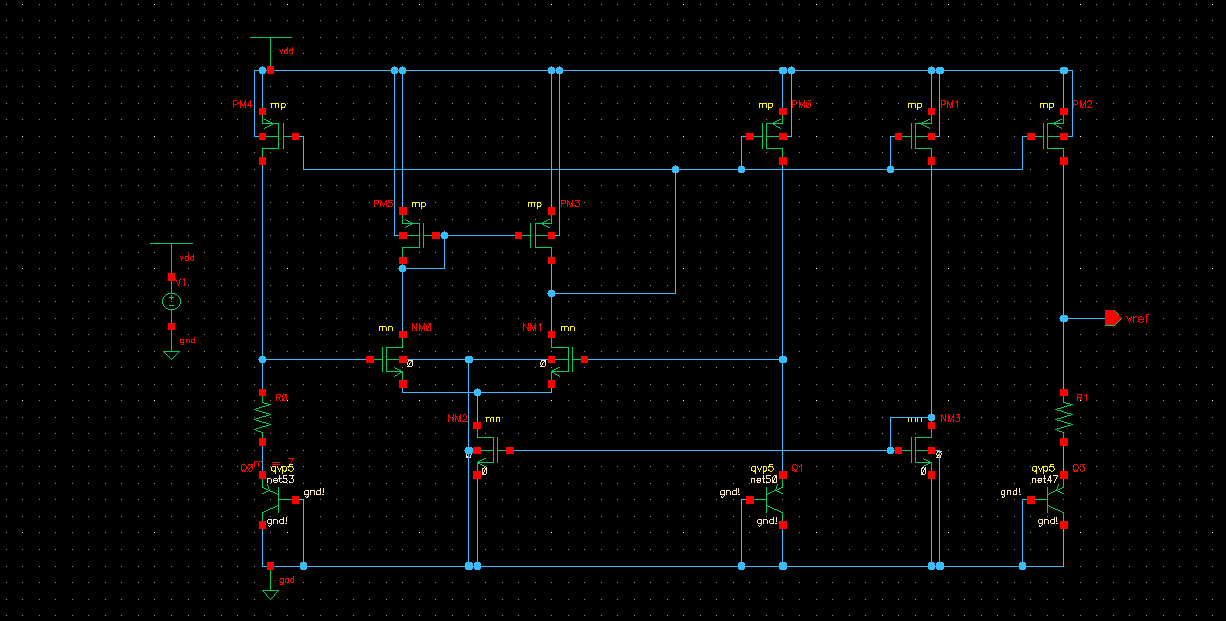

如图为何乐年书上第八章的原理图,参数也照书上给的参数设置。书上给的方法是按图连好后直接dc 温度扫描,然后通过改变2个电阻值来不断优化vref对温度的输出图,通过参数扫描的方法可以得到还不错的输出曲线。

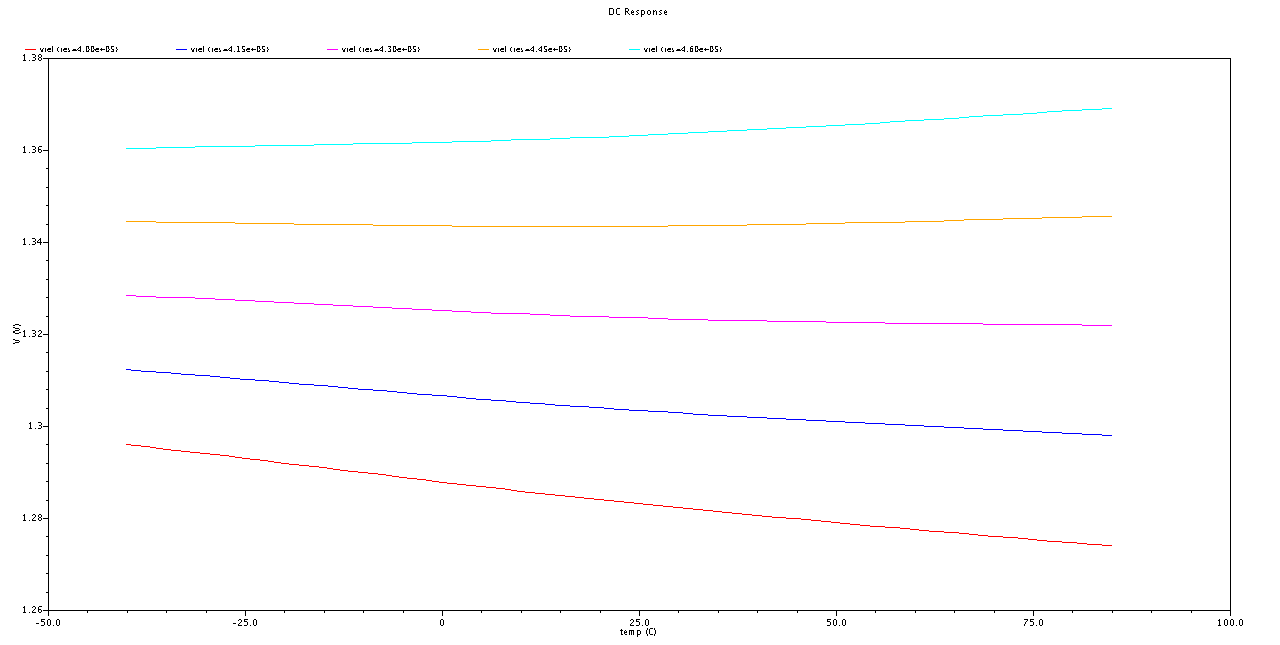

这是2个结果图,有几个问题想请教

这是2个结果图,有几个问题想请教1 对电路做op仿真,发现由于电阻R0取26k,I很小,使得不少管子进入亚域区,觉得不合理,运放的话肯定期望增益越大越好吧?(但是仿真结果好像还挺合理。)

2 第二个结果图抛物线顶点在下,而一般别的仿真结果都是顶点在上,也就是常温的时候vref是比较高的,不知道这个有没有影响?

还有几个问题请教

带隙基准里面各器件参数是怎么影响带隙基准电压源的性能呢?

1.运放的目的只是为了是两个输入端的电位相等吧?因此是要求增益越高越好?此运放需要补偿吗?

2.各支路电流取值该怎么取呢?电流的大小对电路的影响是?

3.恰当的取两个电阻值的比值可以得到零温度系数的输出电压,可是具体的电阻取值该怎么取呢?电阻太大了占用面积太大,太小了是不是会影响到支路的电流?

亚阈值区也可以把增益做到很大的. 关键是统计仿真能不能满足在工艺波动和失配情况下做到很好的统计分布. 所以还是要看关键晶体管的饱和的.

Min/Max已经差别很小了,所以常温下到底输出多少,或者开口向上向下都不太重要吧.

3q,书上光讲软件使用了,不过这些具体仿真的细节书上都没

你做corner了吗?

结果还是很好的话应该问题就不大

确实VREF值有点奇怪

Pennisi <<CMOS current amplifiers>>1999

学习一下

你的意思是vref偏大了吧,应该在1.2V?我没做corner,感觉电路都还么调好。

这个作者的和1999年的文章只有3篇A versatile

CMOS fully differential current

amplifier

High-speed voltage buffers for the experimental characterization of

CMOS transconductance operational amplifiers

A class AB CMOS current mirror with low-voltage capability

我想问小编你最后是怎么解决的,几年了应该解决了吧。

意思是vref偏大了

1. 差分对管进入亚阈区很正常,为了减小运放的失调电压,Sansen的书上也有提到

2. 使用CSMC 工艺,VBG曲线的确会开口朝上,这个没关系

后面我上论坛求助了,结果有个大神回答了,他说是因为Vbe的温度系数是斜向下,而电阻的温度系数也是斜向下。这样两系数叠加后会造成影响。我后面也测了P管的温度系数,结果也是向下,这样在图中斜向上的温度系数曲线只有不同的双极型三级管间的温度系数了。我觉得斜向下的温度系数有点大,应该要调小它。最后我调P管的宽长比调到最大,不再影响电流,尽量避免影响电路,最后它的开口可以向上了。但是它的输出电压比正常的输出电压低了。我工艺用的是SIMC18的。顺带问下小编,可否有提高输出电压的方法。