sar adc offset

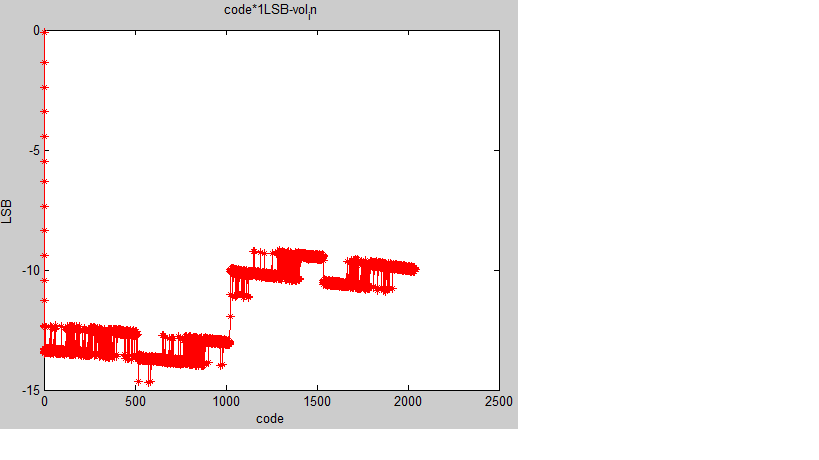

各位前辈,最近第一次做了个11bit SAR-ADC,测试发现offset较大,测试方法就是外部用一个可编程电源,外灌2048个台阶的模拟电平,

然后让 ADC 依次转换这2048个电平数码,用转换后数码数值与外灌模拟电平相减,发现差别竞可达13LSB,下图是测试结果,请问各位前辈,

这种偏差一般多大合理?

先输入0,看输出此时offset是多少。另外offset 13LSB如果和你设计的差不多也正常。

看你内部有没有offset消除电路,13LSB的offset已经很小了

應該沒考慮 process 偏差吧 !

你好,内部所用比较器是带有offset消除功能,结构就是常用的 preamp+cap+amp+cap+amp结构。电路前仿真和后仿真转换出来的编码数值与输入模拟电平基本没有偏差啊,第一次做 SAR ADC,感觉 13 LSB offset 比较大的啊。检查 layout ,

只是发现比较器部分 layout ,有些地方没有形成闭合的 guard ring,这个有影响么? 看过 TI ADC data sheet, 12bit SAR ADC,

offset 数值范围为 -3.5LSB ~ 3.5LSB,请问前辈你之前做的 类似 ADC offset 可达多少? 另外说明一下可编程电源纹波约 1mv,

根据记录到的输入模拟电平数值,可观察到输入电源 DNL 约 -0.5LSB ~ 0.5LSB。

前辈,你好,我的前仿真和后仿真结果都没有看到转换码数与输入模拟电平存在这么大 offset,后仿真也就是约3mv偏差, 所用比较器是常用带有offset 消除功能,我看到TI 12bit SAR ADC ADS7953 data sheet,offset是 -3.5LSB ~ 3.5LSB。另外说明一下,测试板上输入通道路径上靠近信号Pin 漏焊了低通滤波电容,可能有一定影响。因为直接测试板上带有104电容的 vref电平时,offset数值还有约7LSB。请问你做过类似分辨率ADC,offset 可做到多少?

前辈,你好,我的前仿真和后仿真结果都没有看到转换码数与输入模拟电平存在这么大 offset,后仿真也就是约3mv偏差, 所用比较器是常用带有offset 消除功能,请问所说的process偏差是对哪部分功能模块影响? 比较器? 电容阵列? 还是 ?

如果没有失调消除电路的话,13LSB的失调算是小的了。但是加了失调消除电路,理论上不该再有这么大了吧。2~3个LSB那算是正常的吧。请各位指点

带有offset消除电路的比较器,应该不会有这么大失调的吧。

比较器是带有offset消除功能?

每个芯片都是这么大吗?13LSB是不是固定的?你试试修改测试方案。输入直接短路到一起是什么情况?

whoknow it ?!

sar adc offset