PLL锁定后vco控制电压的问题!

不好意思,刚才上传的图片不清晰,重新上传一下:

用conservative精度试试,估计只是仿真误差

感觉应该不是仿真精度的关系吧,我的Accuracy Defaults这没有选,Options里面time step parameters的step和maxstep都设为了0.03ns,这个精度按理说应该足够了吧。(整个pll里面最高频率为3G)

感觉正常现象

您有没有做过PLL呢?这种现象会影响VCO输出信号的中心频率还是它的的相位噪声?或者基本不会有什么影响?

正常现象,放大了看都会有ripple

自己算一下频率/周期变化有多大,电压*Kvco

仿真器误差,cp mismatch都会使得up/down pulse产生,如果不产生up/down怎么能正常工作呢

不过这些仿真中出现的比起实际中那些jitter带来的up/down都是小case

应该是正常的,PLL锁定本来就是一个动态的过程。

不过如果你什么都设置定好的话,仿真应该能看到一个周期性的波动,虽然很小,但应该是有的。

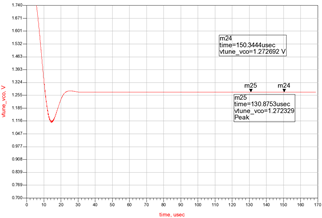

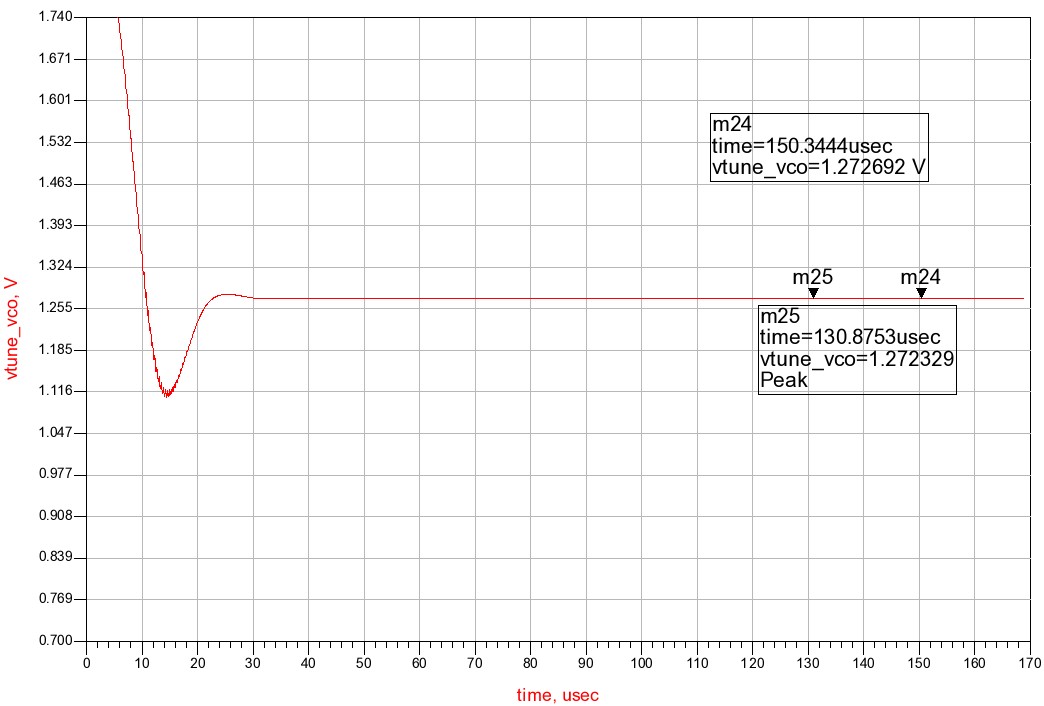

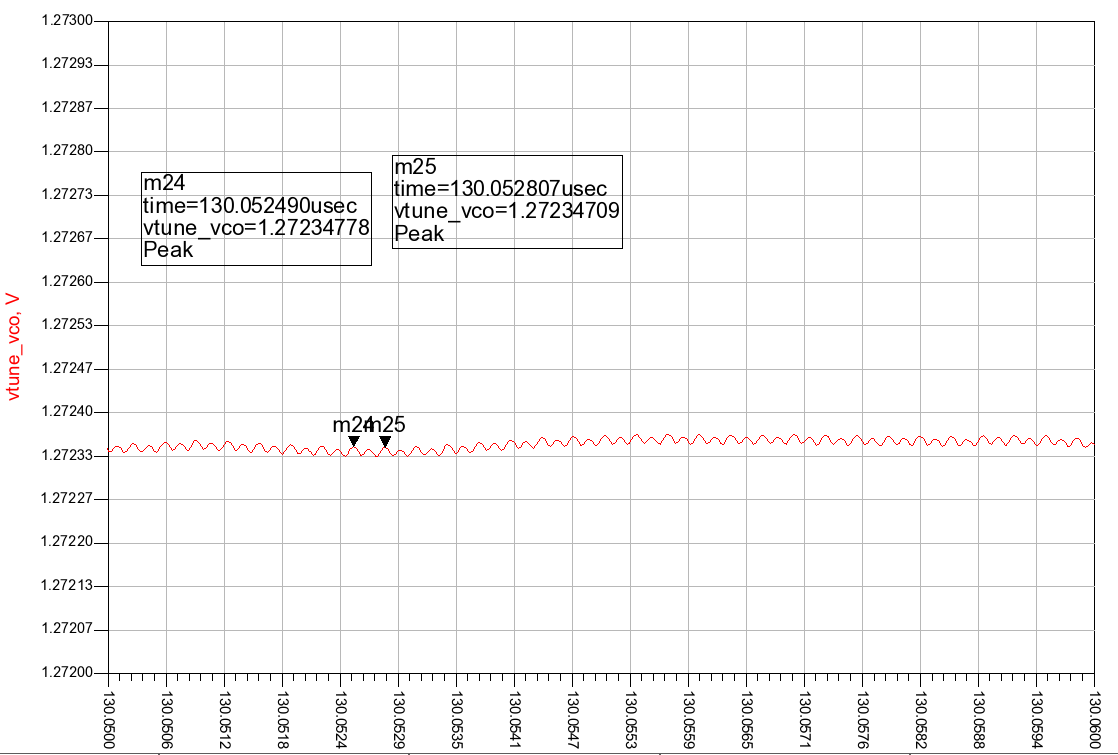

首先谢谢您的回答。1.您说的ripple应该是下图中所示的这种现象,把时间轴也拉开,可看到VCO控制电压上面有频率等于VCO输出频率的ripple,不过这个ripple的幅度只有约十几个uV,幅值很小,而且这种ripple应该是属于正常现象。

2.我在2楼展示的图想说的意思是,它从40us到170us这样一个很长的时间区间内一直在乱七八糟的上升下降,这个浮动的范围有约1mV(如2楼图所示),这个变动应该不是ripple,因为它的变化很没有规律。而上面说的ripple在这么长的时间区间内应该可以看作是2楼图中那条在乱跳的线的粗细。也就是说,我想问的是,这条粗细为十几uV(ripple大小)的线,在1mV的范围内跳动,属于正常现象吗?会对输出频率造成哪些影响呢?

3. 我的仿真步长设置的是pll里面频率最高的信号周期的十分之一,这个精度感觉应该足够了呀,会是仿真精度导致的误差吗?要不要把步长再减小试试呢?

说的有点多,恳求您能百忙中抽出时间帮我解惑,小弟感激不尽~

您可能也误会了我说的意思,麻烦您看一下我在9楼回复的内容哈~

不是要看vco频率的ripple,要看ref clock 频率,也就是PFD频率

看charge pump的up/down

Vcontrol变化会引起spur。另外,我有没有做过PLL不重要~

vtune上面频率等于PFD输入频率的ripple的确会引起VCO输出频谱两侧出现参考杂散。不过如果vtune电压一直在某一小范围内变化呢,会不会引起VCO输出频谱的中心频率一直在变呢?我说的这个小变化不是ripple哈~

VCO控制电压上出现规则的纹波是会引起参考杂散,但如果是像我这种毫无规律波动呢?

这是正常的,从图上看这些都是很低频的波动,滤波器滤不掉的。也可能和VCO的线性度有关。

您这句“和VCO线性度有关”倒是提醒了我...因为VCO各点处斜率其实是有区别的...这种现象属于正常现象,就是说它不影响VCO输出频率的纯净度对吗?

不知道你后来是怎么解决的?我也遇到这样的问题,整个环路的设置在matlab建模中都没有问题,相位欲度是60,KVCO=60,输出频率是36M,如果抖动有1mV,精度太低了,肯定是有问题的。CP和PFD的范围都没有问题,DN和UP的sink和charge电流误差在一个cycle中平均都是100pA级别的,不知道是哪里问题?

你可以画一个眼图看一下它对jitter的影响。我感觉是仿真器问题。

是小数分频吗 感觉像是小数分频的原因,相位变化比较大