聊聊电流镜(下)

上期我们聊到了电流镜的常见结构,错过的可以回顾一下。

http://bbs.eetop.cn/thread-623248-1-1.html

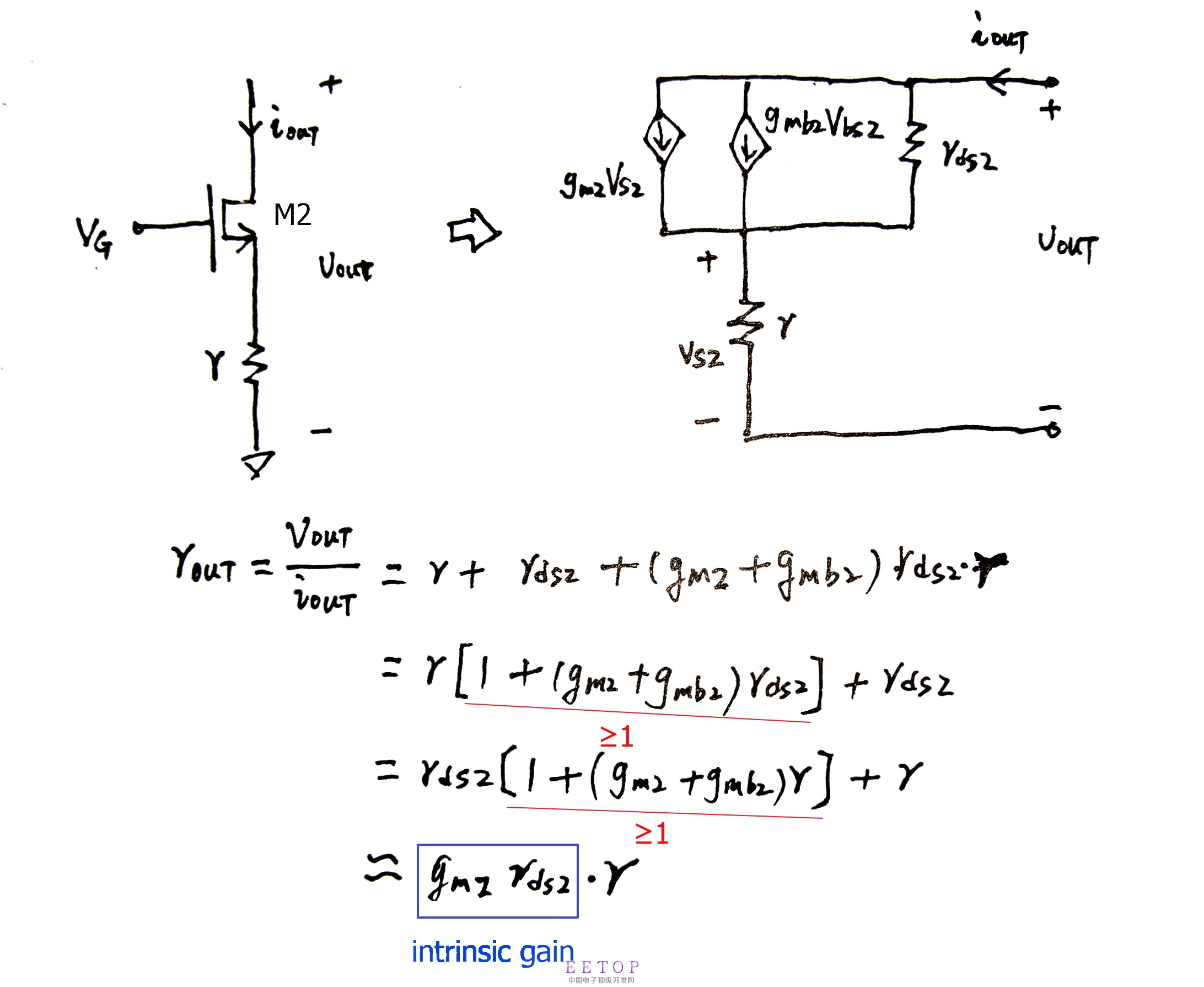

接上期,我们都知道,利用图1中级联结构,可以有效地提高其小信号输出阻抗,其输出阻抗增加的倍数约为gm2rds2,约为共栅管M2的本征增益。该本征增益通常会远远大于1。

图1

上期中的图(i)的源极退化电流镜结构就是通过源极的串联电阻,提高整体的输出阻抗,但存在着比较明显的缺点,该电阻通常较大,会显著减小输出电压摆幅。

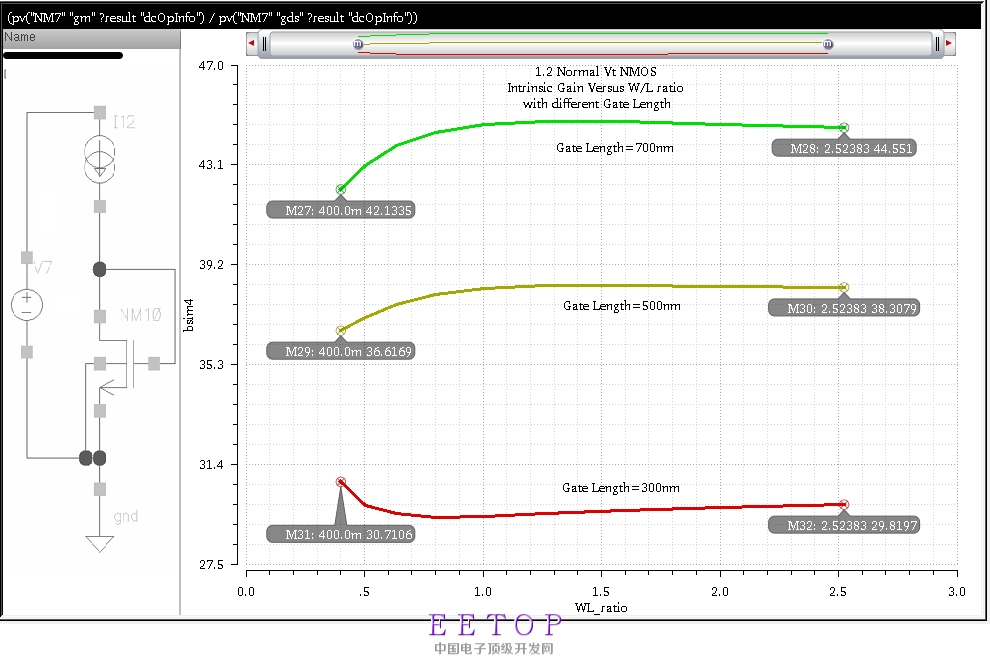

利用某Foundry的90nm工艺节点模型,图2为1.2V标准阈值器件的本征增益和沟道长度的关系。一般来说,栅长越大,其本征增益越高,

图2

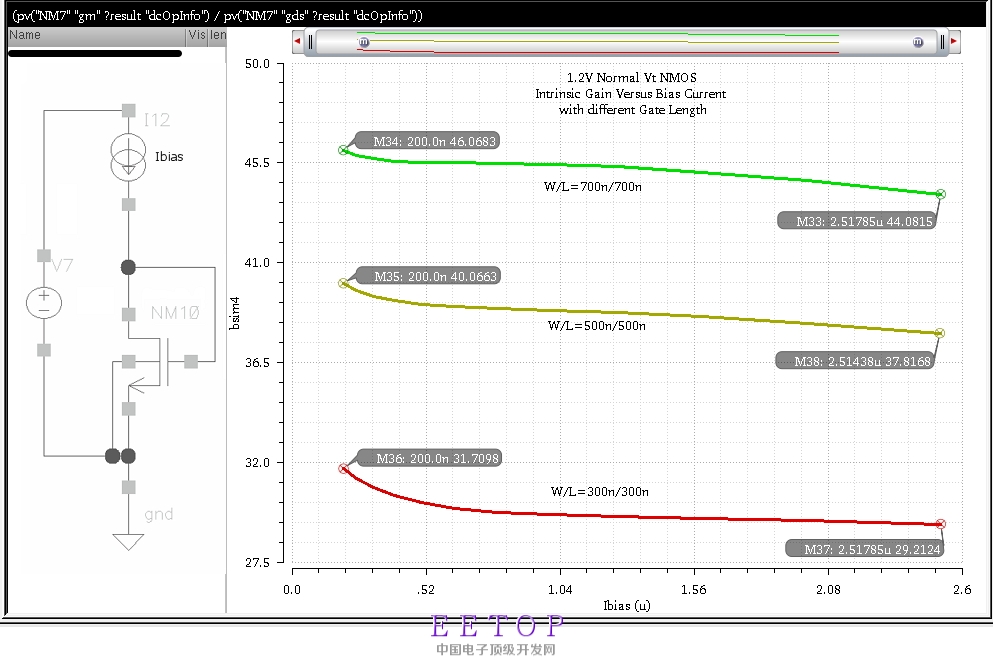

对于固定W和L,图3中,增大的偏置电流会使器件从弱反到强反型,从而使器件从亚阈值区进入饱和区。其本征增益会稍微减小,如图3所示。

图3

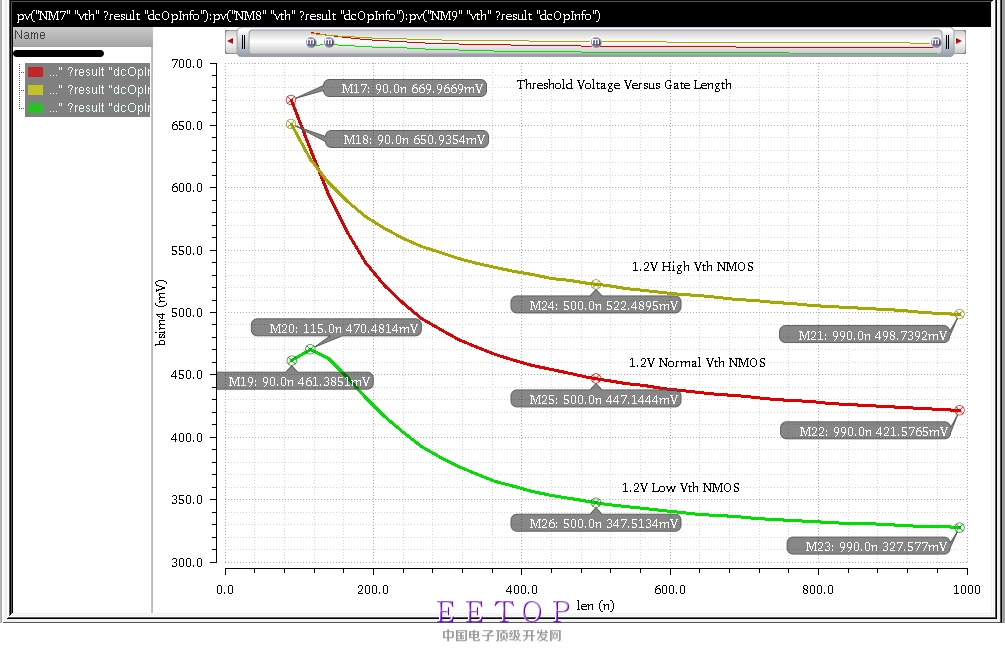

器件的阈值和栅长密切相关,表现为反向短沟道效应(Reverse short-channel effect)。图4是低阈值、标准阈值和高阈值1.2V器件的阈值变化情况。随着栅长的减小,阈值都有不同程度的增加。这也是先进工艺中,电源电压在下降,但模拟电路中选择的器件栅长并不能按比例shrink缩小的原因。

图4

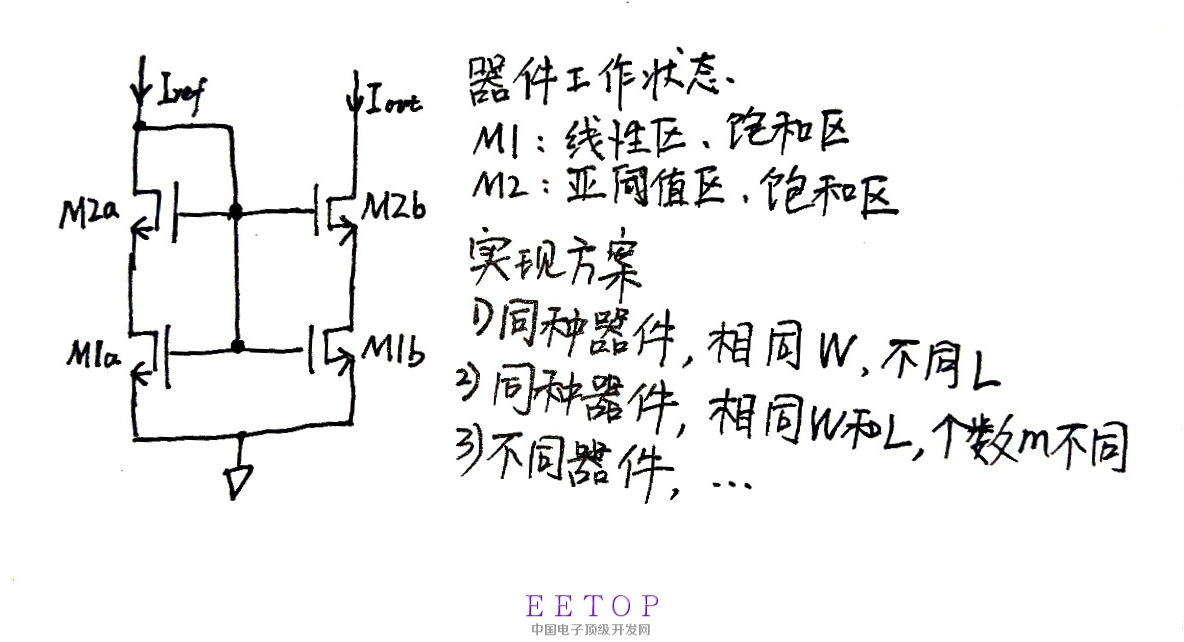

图5列出了Self Cascode CM的实现思路及方式。这里提出了几种可能,其中方案1)利用同一类型器件不同L去实现,也是Ichiro专利提到的思路。其中方案2)也是目前文献中提到的性能较好实现方式。方案3)是我想到的利用部分工艺提供的不同阈值的器件组合来实现。

图5

下边具体分析下,上述3种实现方案。

1)Ichiro在其专利中提到的方法,其解释是利用M2的沟道比M1的沟道短

,从而M2管阈值小于M1管,利用阈值差,使M1工作在临界饱和,从而得到较大的输出阻抗。

注:在这一点上我保留意见,因为先进工艺中往往表现出RSCE使得短沟道具有较大的阈值。

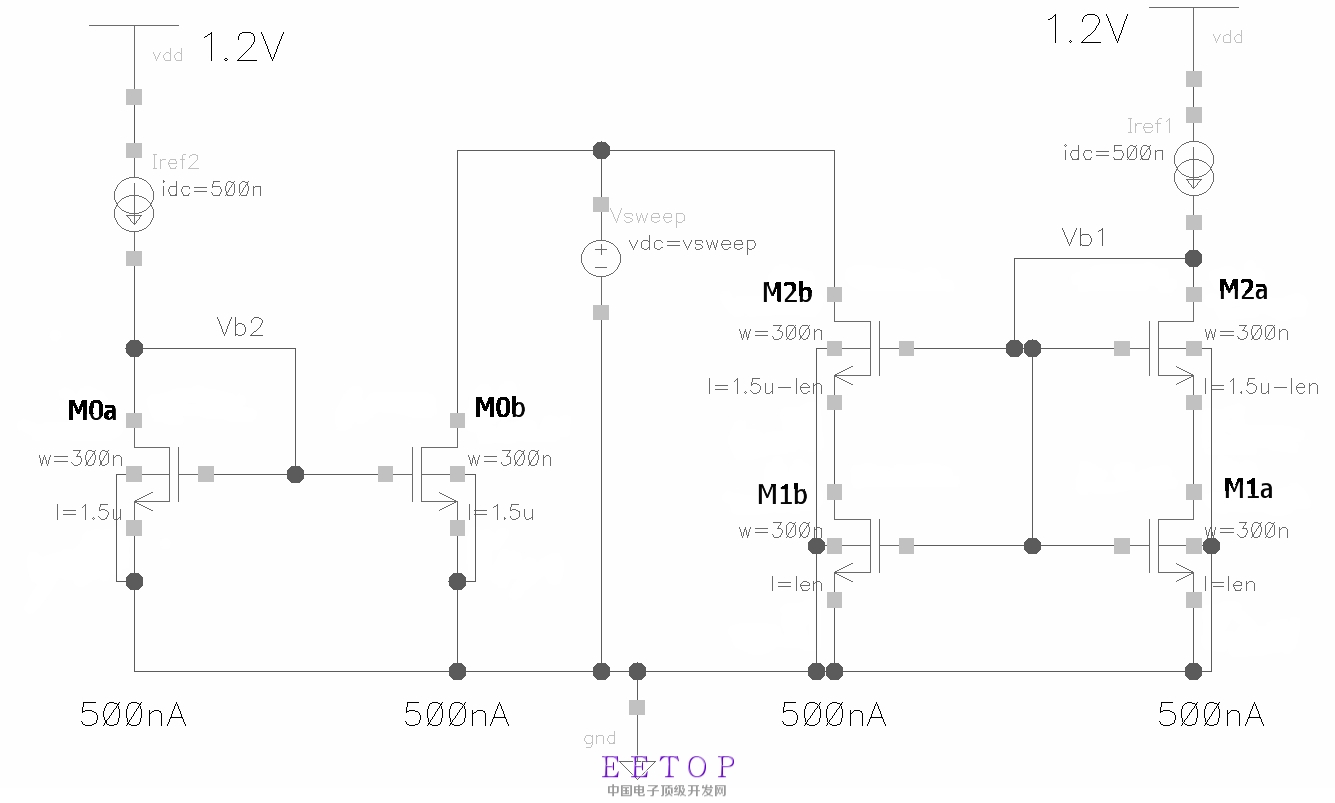

这里对比了同样面积条件下单管和拆分的管子的I-V特性。测试环境如图6所示后续也会用到这个测试电路作为对比。这里选择了W=0.3u,总的栅长L=1.5u,镜像500nA的电流。实际应用中根据需要,选择合适的尺寸。

图6

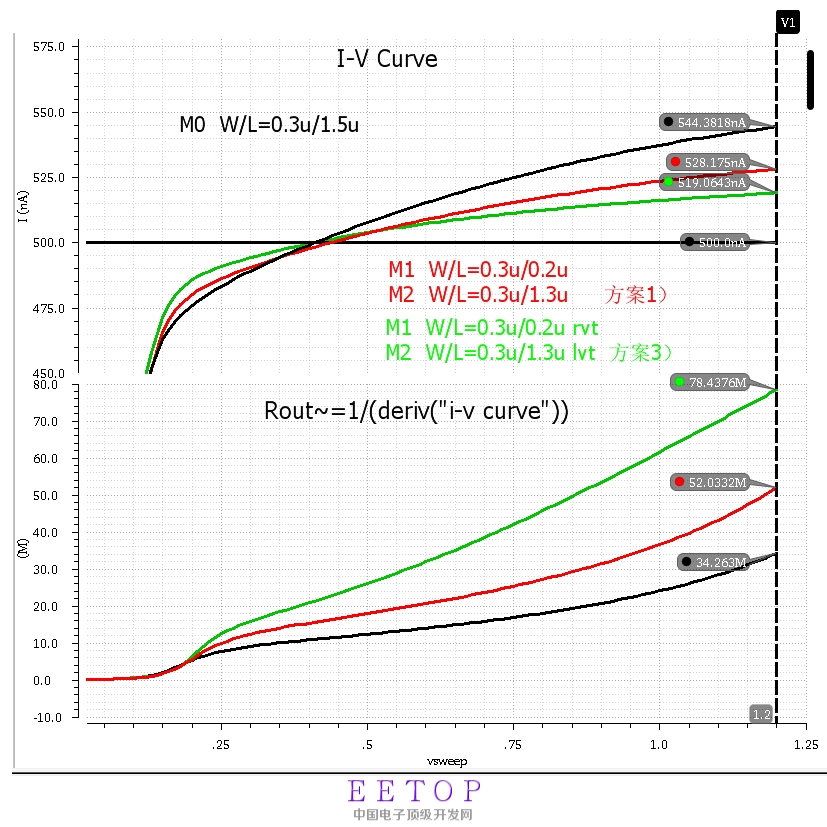

图7是方案1)中,I-V特性的对比,其中黑色为单管M0b的漏极电流;红色、黄色和绿色为不同尺寸拆分情况下M2b的漏极电流。

红色情况下输出阻抗提升比较明显,这也是最简单的一种self cascode结构,通过拆分,能够提高输出阻抗。注意,这种情况下,M1管沟道较短,其阈值较M2管大很多。当总的栅长较大时,情况会稍有不同,阈值差别不大,需要用方案2)来实现。

图7

2)这也是一种常见的实现方式,M1管和M2管尺寸相同,M2管个数是M1的整数倍m。

同样利用图6的测试环境,这次M0、M1和M2的W/L=0.3/1.5u,改变M2和M1的个数比。得到如图8所示的I-V特性。

图8

虽然对比有些不公平,毕竟面积大很多,但可以看到这种方式还是能够大幅度的提高其输出阻抗,并表现出了较小的饱和电压从而增大了输出摆幅。其中M1工作在线性区或临界饱和,M2一般会工作在亚阈值区。

图9

图9是一种版图实现方式,这里M2和M1的比例为3:1。

3)方案3)的实现方式,适用于提供的多种阈值的逻辑器件(90nm以下)的工艺。从图4看到,hvt器件阈值会比rvt多出几十毫伏电压。利用阈值差,可以促使M1管工作在临界饱和区,从而得到较大的输出阻抗。

图10

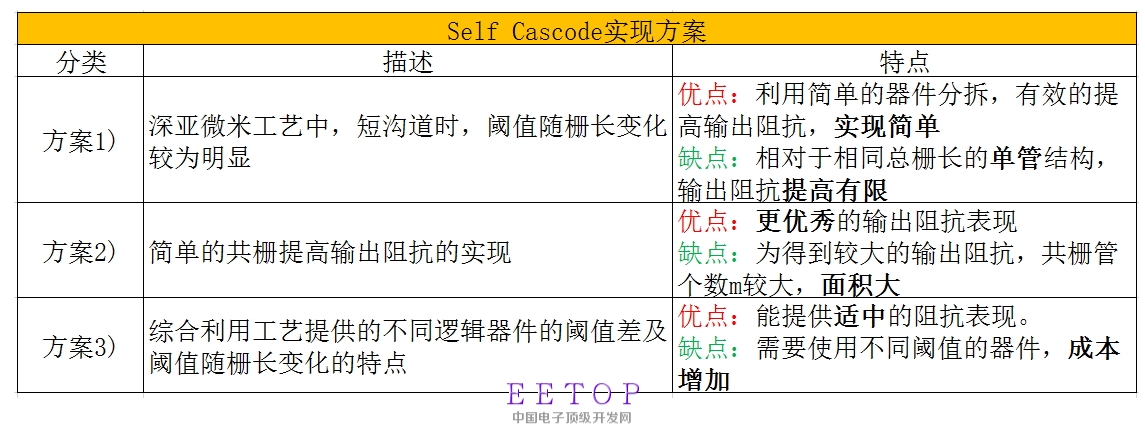

总结图5中的方案的优缺点如下图表所示。实际应用中需要根据情况选择。多实践,多总结。

图11

好了,这期的内容的就到这里了,下次再见。

也请关注俺的微信公众号,能第一时间看到我的学习分享内容哟~

不错,kankan

thanks for sharing

小编有心了,请问这个是你转载的还是你自己编辑的?公众号是你自己在运营么?

自己写的东西,也算是把学习的东西总结一下吧

很不错,可以加个精,我在本版没有权限,我帮你问问其他小编

学习下,自己写的

想问下方案2两个馆子的VTH没差是吧,只是变大m来减小vdsat是吗

谢谢小编。

阈值会有不同,毕竟一般情况下,M2会有体效应的存在,阈值稍大一些

我也看了你的公众号,很好 有没有其他模拟IC公众号让我上下班途中可以看?不想端着一本大书看!

别人的我也不了解,你知道了也请告诉我哈

加油加油,基础的东西还是很重要的。有时候我也想总结总结,就是犯懒。

看看先。

帮顶 支持原创

謝謝! 有用!

在图4上,你有一句话:随着栅长的减小,阈值都有不同的增加。

在图5下,你有一句话:利用M2的沟道比M1的沟道短,从而M2管的阈值小于M1。

这两句是否有矛盾?

另外,为什么增加偏置电流会使本征增益变小?

解释一下,图5下,也就是Ichiro提高的阈值随沟道变小而而变小,我是存有疑问的,(后边有注),Ichiro提到是SCE短沟道效应,要注意他提到这个的背景(1985年提出),那时候半导体工艺可能还是um以上的,随着沟道变短,阈值才会下降。

学习学习

写得很好的总结。感谢小编又让我复习了一遍。

因为我在实际芯片中经常有使用小编重点研究的这种self cascode CM,所以分享下我的观点和操作。

1) 关于小编提及的输入阻抗的问题,我觉得不应该是rds+1/gm,仍是是1/gm;

2) 其实电流镜真正核心的是下面两个管子,所有做的工作都是尽量保证下面两个管子的匹配,包括器件mismatch,包括vgs与vds,只要这些做好了,电流镜像就准确了。

3) cascode主要是层叠一层管子,使得输出阻抗增加,同小编分析的一样,变成gm rds rds。

4)具体到这种self bias cascode CM,我认为设计上应该使得四个管子都工作在饱和区(包括亚阈值),方法就是,下面的管子采取倒比管,上面的管子采取大的W/L。串联管中,粗略等效,等效成一个管子的话,L是相加的,因此总体来说,等效管子也是倒比管, 这样总的等效管子是工作在强反型的饱和区的,而且由于是倒比管,总等效管子的Vgs=vth+vdsat。而对于上面的管子来说,因为大w/l,使得管子被偏置在亚阈值区,vgs<=vth,所以下面管子的大致是等效管子的vdsat(随具体设计)而工作在饱和区。

5) 从电流源的角度来说,输入管子其实就是提供一个偏置电压。

6)从匹配的角度来说,刚好也需要下面管子工作在强反型的饱和区,而从输出阻抗的角度来说,cascode管子刚好最好工作在亚阈值区。一切都是这么统一协调,真是神奇,看上去那么美。

抱歉:一写稍微长点的回复,就有点耐心缺失。没有检查我有没有写清楚,请将就看看。:)

建议包括matching的讨论。

mismatch后续会单独出以一篇内容,专题讨论的

首先谢谢你提了这么多内容,上篇中结构f的输入阻抗确实近似为1/gm,这一点是我理解的有误。self cascode的这种结构的小信号模型近似等于结构e这种共源共栅结构从二极管连接处看到的输入阻抗。也谢谢你现身说法。

你也是个人才

学习了,扎实的理论基础还是很重要的,有时间还是得好好研究研究。

现在基本上产品上用到的电流镜一般结构都是使用单级的NMOS电流镜(设计简单,节省面积)和加res那种self cascode(输出电阻值高,但消耗更大的电压余度),对于后者,在全PVT下一般可以牺牲共栅管(处于线性区),其实共栅管主要的作用就是用来使得最下级一对管子的VDS保持一致,保证电流的准确性。

以前没听说过这种self-biasing的做法,好像挺有意思的,看看