关于电流镜

analogLib库中的理想电流源,取值100uA,我把两个管子W/L设成一样,可是仿真

显示两管的电流不一样,二极管连接的管子电流为理想电流源的值100uA,可是镜像

支路只有40左右,我增大管子,可是调来调去都离100uA差好远,请问这是因为什么问题啊?

是不是我哪里没有注意到什么?

沟道长度调制效应,大哥。

请确认你的op工作点是否正确

被镜像的管子是否工作在饱和区?

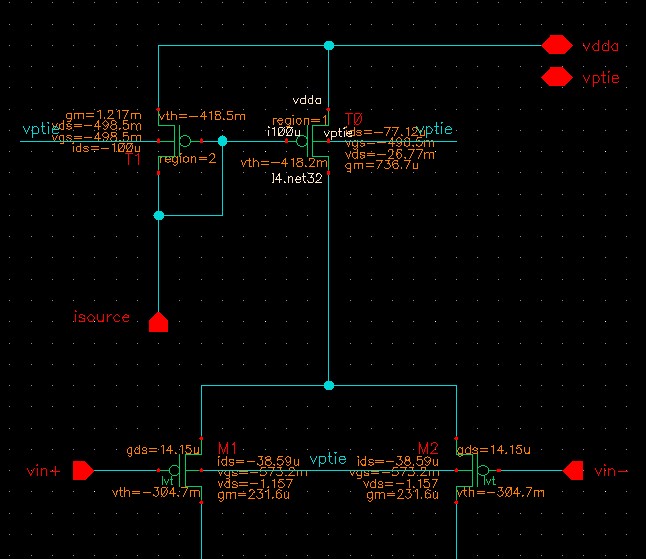

这是我的电路,镜像支路看起是在三极管区,该怎么调才能使其在饱和区呢?

下面的输入管以及其负载是不是也需要调整?

4# 敏兹

the current tail transistor is in linear region.

Do you find its vds is only 26mV?

I think you can reduce input DC level

good thanks

受教了

Vds 太小了吧

右边的PMOS管处于线性区了

楼上正解

多自己调调输入电平吧!

不知你什么工艺,你的电流镜根本就没有实现,右面的管子没有在饱和区,你看看你的输入信号给的是不是有问题,输入差分对也看下吧

为什么要调输入电平么?

我调整过后尾电流源进入饱和区了,但是电流始终只能到85uA左右,而且是把输出共模调整到0.2v左右的结果,感觉差好大啊,本来输出共模应该要0.6才对的

工艺就是0.13u的cmos

输入是Vpp 1v的差分,输入共模也是0.6

13# 敏兹

Please calculate your input and output range carefully.

For the differential pair or opamp, input range will be much smaller than output range. And you can never put the common mode at VDD/2.

I think you should set the input common mode at 0.3V~0.4V when the VDD is 1.2V.

By the way, you should increase your input PMOS size 2 times.

thx,fuyibin

为什么不能把输入共模设为Vdd/2呢,当Vdd=1.2v时

我的输入信号是从采样或者mdac进来的,他们的输出共模就设的是Vdd/2啊。

不过这个工艺下Vth在0.3v左右,我把输入共模调到0.4时确实情况好了很多,但是老师说共模没有多大空间给你变化,所以最好还是保持Vdd/2,那这样严格的情况下,我该怎么做呢?

而且我发现每个管子的宽长比都好大,会占很多面积

差动对管得改改咯。

增加宽长比 或者增加倍增因子 可以减小管子的过驱动电压 有利增加共模输入范围

管子尺寸小了,造成压降过大,自然共模输入范围也受限制;最简单的办法就是从尺寸上着手,毕竟Vth只有0.3还是先天的优势了

不匹配啊

http://types.yuzeli.com/survey/mbti28lone/

op states are the basic of opam working