设计SAR中的比较器时遇到问题

时间:10-02

整理:3721RD

点击:

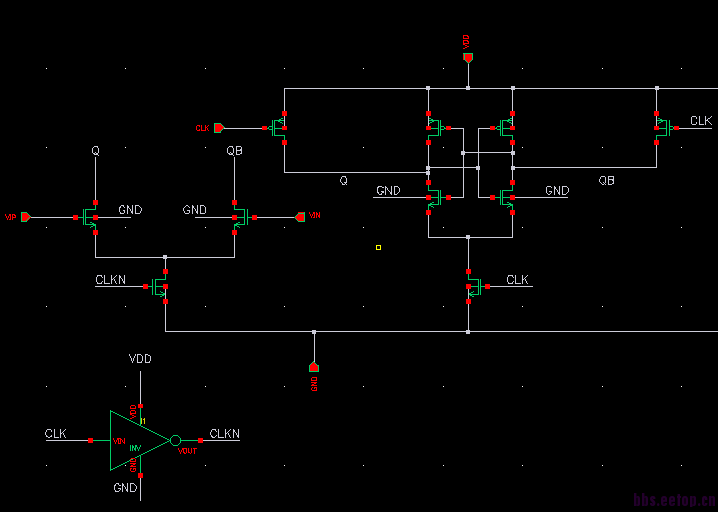

在做SAR ADC的过程中,设计了如图所示的比较器,包括预放大和latch,仿真的时候遇到以下问题,

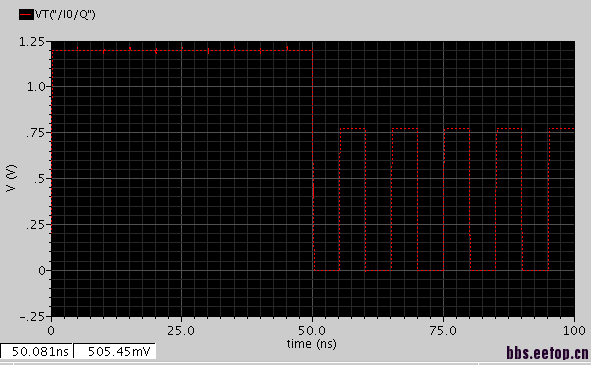

输出Q在低电平出现了很大的类似于时钟的脉冲,请教它是怎么产生的?如何消除?

你应该把你的输入信号和控制时钟波形都给出来,直接一个q的节点,我也不好分析。

这个能工作?为啥不直接用strongarm 结构

刚入手这一块,您说的strongarm我不懂。预防大+latch是可以实现功能的

时钟就是如第二个图中的后半部分,周期10u,幅度从0到1.2V;输入信号是两个相反的脉冲信号,周期100u。第二个图就是仿真了一个周期的脉冲。

baidu 一下 strongArm comparator

你这个电路不是很好。完全靠latch这边的gain,是不太够的。

时钟溃通么,电容耦合过来的时钟信号吧

解决了吗

我最近也要做SAR ADC,学习一下

震荡了吧

你好,我在做动态比较的时候也是遇到预放大器增益上不去的问题,请问有什么好的解决办法没?

有可能是因为刚开始还没有稳定,所以比不出来,求问小编有没有关于SAR ADC中比较器的资料啊,我最近也在做这个,但是觉得不知道如何确定比较器的指标,比如增益,带宽什么的,这是根据什么来确定呢?

正好我也在从比较器入手,我也没有什么资料,你可以看看Allen的书,里面比较器讲的很详细

最近也在用可以給完整一點嗎看不出來問題

好的,谢谢小编啦,一起学习

是不是P管太小了,不能复位到VDD

1111111111111111111111111

学习学习学习了

学习了,感谢分享

应该是kickback noise影响吧

CLK=0 CLKN=1 电路中存在VDD~GND通路,接CLK的PMOS ->差分对->接CLKN的NMOS,Q输出值为VDD电阻分压结果。