电流镜的失调及消除

集成电路中的器件失配(Mismatch)普遍存在。特别是在先进制程中,当工艺的特征尺寸(feature size)逼近原子的物理尺寸以及光刻机射线的波长时,器件沟道长度和宽度的偏差(Variation)的相对比例会逐渐增大。工艺流程中湿度,温度等各种因素都会对器件的参数变化有影响。

可以这样说,即使在同一个die里,设计相同的器件,经过制造过程,总是存在着多多少少的差异。

代工厂(Foundry)通过对工艺流程的严格把控,尽可能的把偏差降低到比较小的范围。图1是芯片的生产过程中,存在的Die-to-Die,Wafer-to-Wafer,Lot-to-Lot的差异。Foundry提供的器件Model中,通常都会把这些偏差进行建模等效,协助工程师进行电路设计。

图1

失配通常会对模拟电路有很大影响,在设计阶段需要充分考虑。比如表现为运放的输入失调电压,电流镜的镜像误差。也可能导致量产时候良率损失的重要因素。

在许多高精度电路设计中,运放或比较器几毫伏的失调,可能会导致系统出现异常功能。电路设计过程中,需要充分失调来源及其影响。考虑失调的消除方式和代价。

当然Mismatch通常都可以通过电路和版图的优化设计,来减小。这就需要在失调电路所需的成本和对电路性能提高之间折衷。

本期仍以电流镜为例,简单讨论下其失调来源及消除方式,作为电流镜系列聊聊电流镜(上)和聊聊电流镜(下)的补充内容吧。

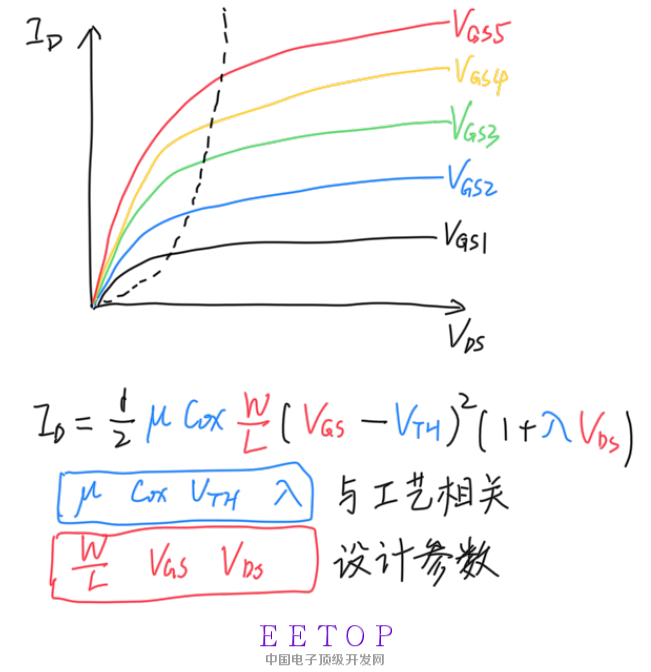

如图2,从MOSFET器件的长沟道模型I-V公式来看。其中影响参数包括u,Cox,W/L, Vth,VDS,λ等,存在着随机或系统失配,

图2

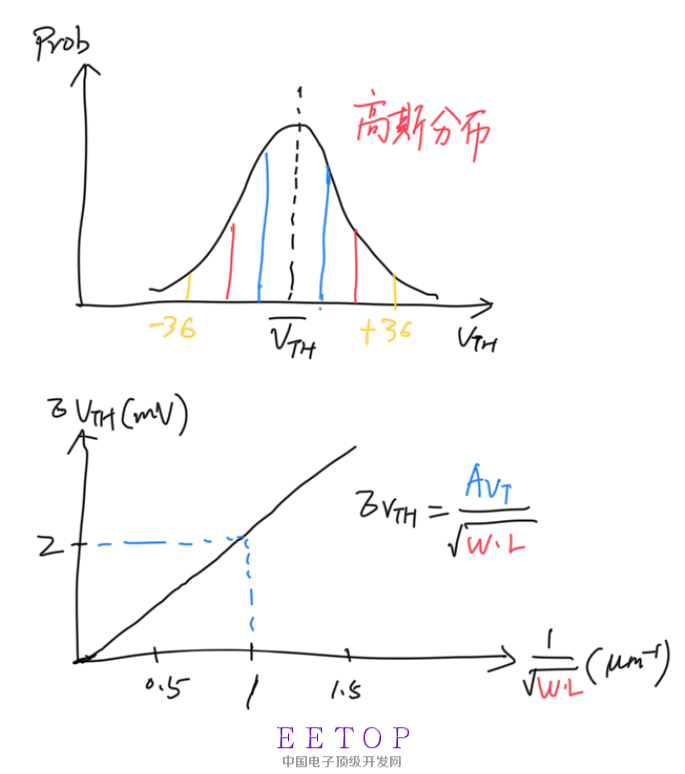

阈值VTH算是器件最重要的参数了,工艺流程中,通常都有阈值调整的Mask,从而保证阈值符合预期。尽管如此,实际的阈值仍然存在着接近高斯分布的偏差,如图3。偏差量的标准差和器件面积的关系可以用AVT的参数表示。

图3

假如AVT=2mVum,如果MOS器件的WL=1um^2,则通过计算简单估算阈值失配3σ(VTH)=6mV。

除了阈值VTH,其他工艺参数也存在随机分布的情况。比如工艺提供的测试结果通常会包含VTH_gm、Idsat、Δβ/β等的偏差计算公式,帮助设计人员选择器件尺寸。当然除了MOSFET外,电阻,二极管,三极管,电容都存在偏差,各种器件的偏差,对构成的复杂电路系统的影响,通常需要借助EDA工具协助分析和评估。

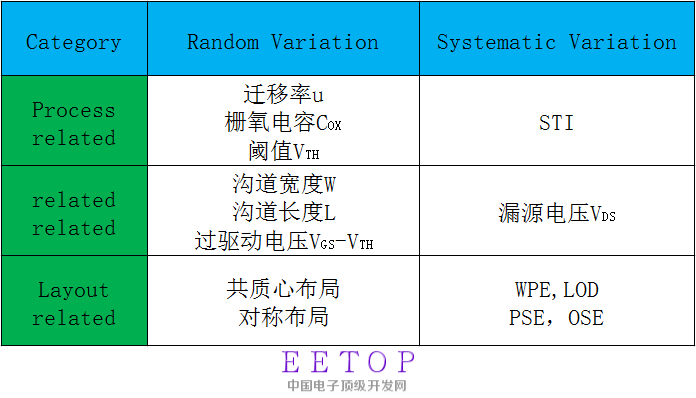

实际上,在先进工艺节点中(40nm以下),和版图相关的效应,如LOD、WPE、PSE、OSE及DFM、STI等都对器件有着比较明显的影响,可能导致失配。图4列出了造成失配的可能因素。

图4

对于简单的电流镜,我们分析一下失配对于镜像比率偏差的影响,以及考虑如何减小其影响。如图5,其中β和VTH都可以通过增大面积减小失配的标准差,并且通过增加过驱动电压VGS-VTH可以减小阈值偏差对总电流偏差的贡献。

图5

那么问题来了,有哪些方法可以提高电流镜像的准确度那?如图6所示。

图6

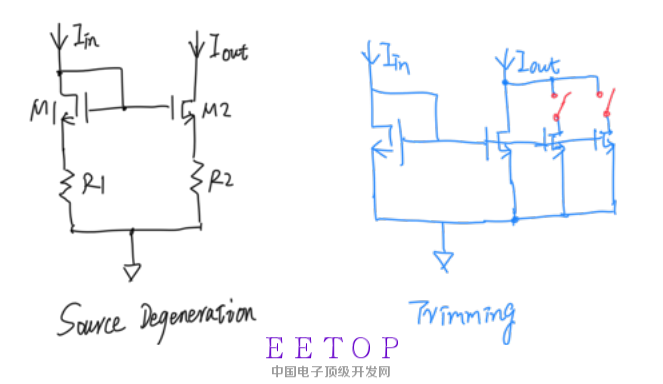

方法1就是通过牺牲面积和电压裕度尽可能的提高匹配精度。方法2和方法3分别通过源极退化和trimming方式,减小失配,提高镜像精度,实现方式如图7所示。

图7

方法4的动态元件匹配(Dynamic Element Matching)算是一种比较进阶的提高匹配精度的方式。下面以1:1的例子说明DEM的原理(1:1时,也称之为Chopping)。

如图8所示,通过时序控制开关,切换M1和M2分别作为输入和输出管子。其中Φ和Φn是占空比为50%的时钟信号,如果M1和M2存在ΔI的失配电流。输出电流Iout具有幅度为ΔI的纹波(Ripple),纹波频率和时钟信号频率一致。从时域上理解,通过切换镜像管,相当于求平均值,消除失配量。

注意,时钟本身占空比偏离50%,也会导致失配ΔI无法完全消除。

图8

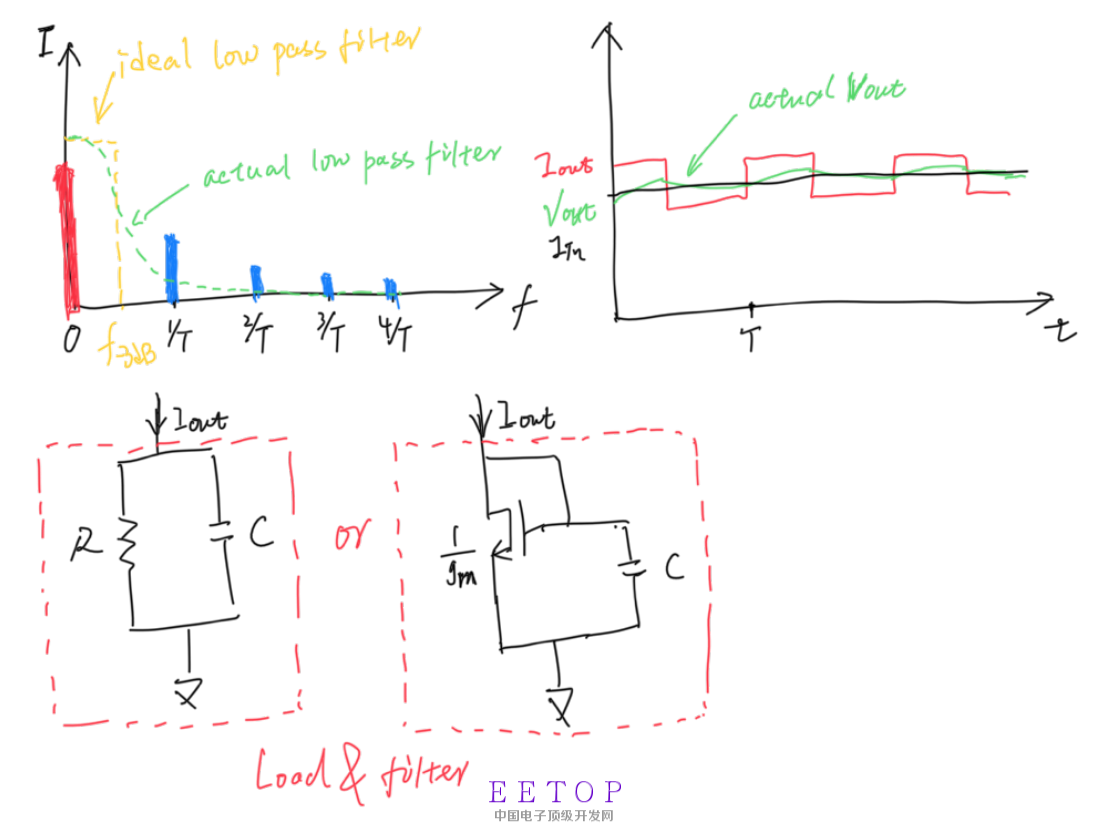

从频域上理解,如图9,就是将失配量调制傅里叶变换到较高频率,失调量表现为谐波分量的能量。可通过低通滤波器滤出失配量。由于滤波器的非理想特性,需要设置好其带宽,将高频失配分量尽可能的衰减到较低的幅度。从时域上看到的纹波就会变得较小。

其中滤波器是结合负载实现的,主要是decap电容和负载形成的RC低通滤波。

图9

DEM同样可以用在1:N、M:N的镜像关系中时,这时需要时钟电路配合,产生特定的控制时序,通过轮源切换的方式,动态消除镜像器件的失配量。

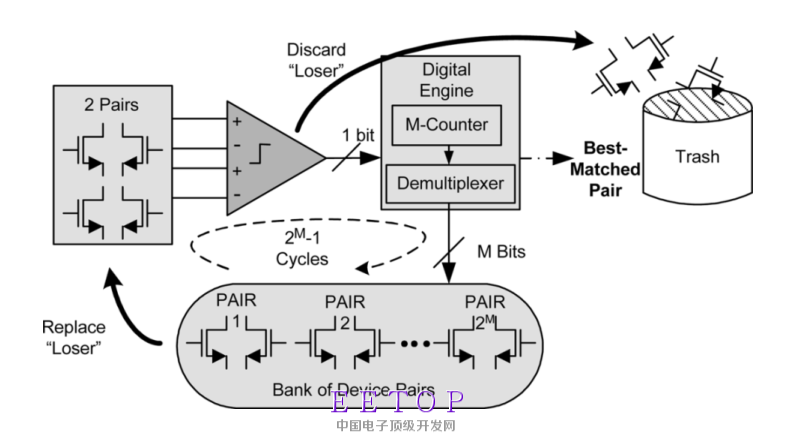

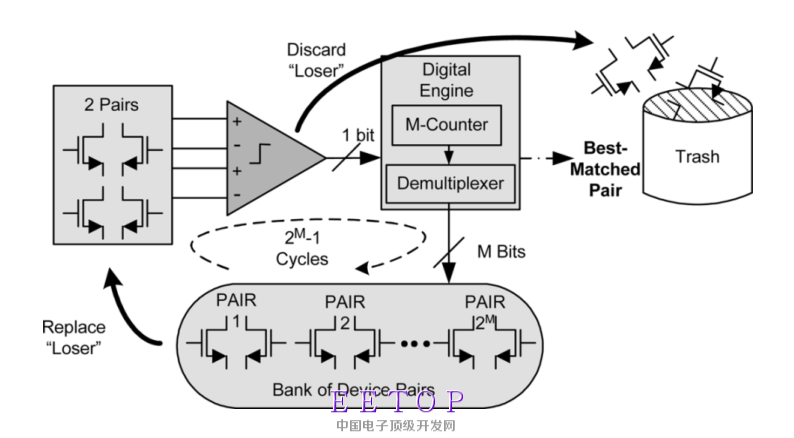

这里给出一个更复杂的匹配方法。如图10,也就是通过比较两个电流镜对,通过在已有的Bank中轮流选择和当前匹配最好的比较,最后剩下的是匹配最好,称之为Survivor方式。参考文献列在最后,有兴趣的可以查阅下原文章。

图10

OK,这期就这么多了,下期我们学习下运放的输入失调及消除方式。

想了解更多内容,欢迎关注小牛牛的公众号,一起学习,进步哟~

图10参考文献:

Vishal Gupta, "Achieving Less Than 2% 3-σ Mismatch With Minimum Channel-Length CMOS Devices." IEEE, 2007

顶一顶,分享分享

写的太好了!已关注公众号,并看完往期内容。加油!

写的太好了!已关注,加油!

谢谢支持

很不错。

很好·

很不错!谢谢!

good!

还可以用运放来钳位左右两个电流镜的drain端,消除lambda的影响。

Thank you for the reply, could you explain more in detailsfor controlling the drain?

thanks