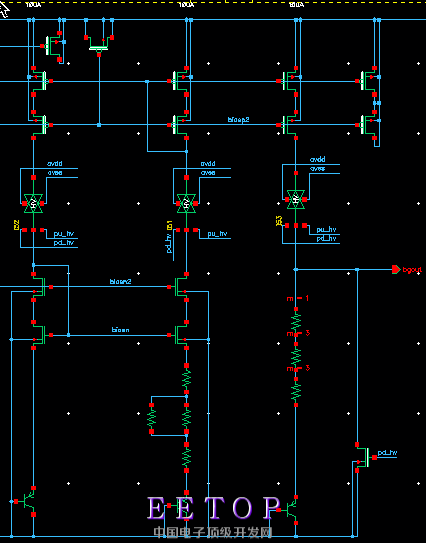

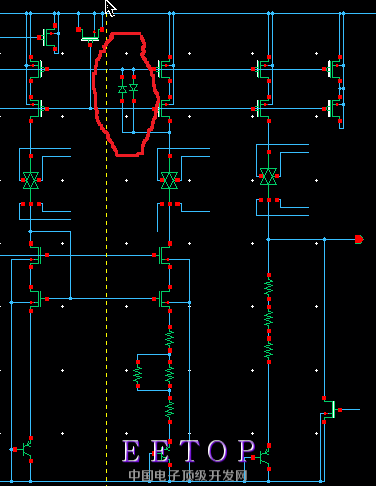

请问这种bandgap降噪方法是否可行?

很好奇diode是如何切断噪声传递路径的,原理是什么,另外,diode本身引入的白噪,散射噪声,闪烁噪声怎么处理呢?

我擦,这图一看就是RDA的路子啊。

不可以,那两个diode会阻断你的DC bias 通路。再说你这个diode怎么做,如果是用mos做,其实是电阻的功能。但是可以把他们换成RC filter。

能看出出处?

哈哈哈哈哈哈哈哈哈……你怎么看出来的

diode两端压差大于阈值时,当作导线提供偏置;当压差小于阈值时,看作开路,隔离噪声;noise summry显示diode基本不引入噪声

BOSS也是说怕影响偏置!

但事实是当diode两端压差大于阈值时,不论哪一端更大,都可以导通提供偏置;而且由于支路电流由BJT和Res决定,上端的偏置电压会非常精确地确定,而下端的偏置电压被diode隔离后,会偏大,但是不会影响正常工作。用MOS连接完全可行,只是需要将sub接源……

以上是我的理解和仿真情况,请大神进一步分析和质疑

1.BOSS也是说怕影响偏置!

2.但事实是当diode两端压差大于阈值时,不论哪一端更大,都可以导通提供偏置;而且由于支路电流由BJT和Res决定,上端的偏置电压会非常精确地确定,而下端的偏置电压被diode隔离后,会偏大,但是不会影响正常工作。3.用MOS连接完全可行,只是需要将sub接源……

4.RC fileter需要的电阻、电容太大,面积代价太大,而且经过实际仿真改善效果没有该方法明显。

以上是我的理解和仿真情况,请大神进一步分析和质疑

如果是MOS应该可以,等效为大电阻。理想二极管肯定不行。

请问,NMOS的偏置是否可以采用相同处理?

我只是想不通RDA现在怎么还在用IBM的工艺?

感觉会出问题。比如给gate节点加个干扰再仿真对比一下。原电路gate对地电阻很小,电平基本被固定。新电路理论上二极管两端电压相等,但一旦有干扰,二极管很难提供电流,只有gate电压多跑0.6V以上才会近似固定住。

很常见啊,很多仪表或者音频前置放大都用这种方法降噪,不过瞬态响应变差,此gate容易受干扰

试过,但是对噪声基本没改善;你可以这样理解,最下面的NMOS的噪声是通过右侧cascode结构放大到上端的,而不是走左侧的导线连接,因为一般论文噪声都是等效为与栅极串联的电压源,从左侧上去没法继续向输出端等效传导。个人理解,多多交流

IBM的工艺?IBM用过这种电路结构?PS:这里用的是smic的工艺

给gate端加0或avdd的initial,都能快速稳定到其正确的偏置电压,而且非常精确(因为是由支路电流决定的);该电路是有startup的,所以我个人觉得,如果gate偏置偏高会被startup拉低,如果偏低会被二极管充电(二极管另一端稳定电压会保持倍gate端高)

终于有大神见过这种结构了!我试过,给gate端加0或avdd的initial,都能快速稳定到其正确的偏置电压,而且非常精确(因为是由支路电流决定的);该电路是有startup的,所以我个人觉得,如果gate偏置偏高会被startup拉低,如果偏低会被二极管充电(二极管另一端稳定电压会保持倍gate端高)请问小编,如果这种方法这么高效,而又基本不牺牲稳定性,为什么bandgap中没人用这种结构(无文献资料)?

电路没撒问题 ,双向二极管做切割。1/f和部分噪声没法使二极管导通,MOS 管栅端没电流(漏电大的低节点工艺估计要小心)。大干扰瞬态的时候也能被钳位到0.6。再进入反馈恢复状态。我只是有个疑问,这玩意能把rc省掉吗。不说外置C了。里面要是放个几百K电阻,50P电容效果也比它好吧。

这种结构下,在gate线上加电容,会进一步降噪……电阻的应该不用加了,这种隔离结构本身又可以带来大电阻,貌似。做过比较,不加diode时,加电容的影响很小

很怀疑,流片结果报告下。

mark,学习

我觉得这个就是利用截止形成的高阻做rc滤波,滤掉噪声效果和rc差不多的,只不过利用二极管或者mos管特性节省面积罢了。滤除噪声优于rc,但抗干扰不如rc,毕竟当干扰大于开启电压或者高频的时候就变成了低阻了。电位恢复很快我不是很理解,可能是gate电容比较小看不出来吧

我也认为容易受到干扰,这个电路的PSRR特性估计好不了

哥们你发私信问我,又拒绝别人给你发私信,我怎么回复你?