请教几个LDO仿真时遇到的问题

时间:10-02

整理:3721RD

点击:

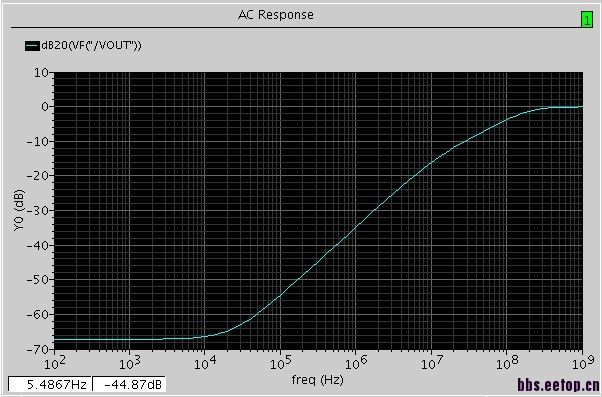

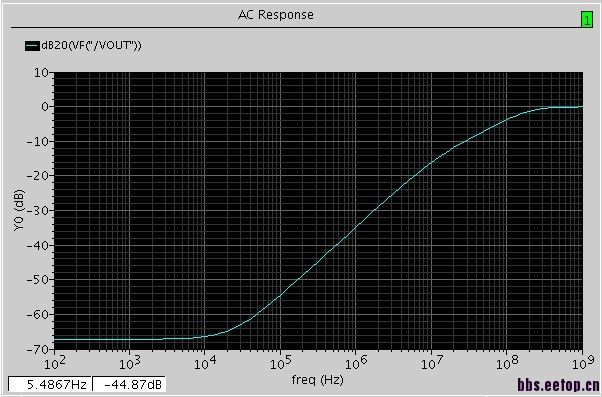

我用folded cascode+功率级接成反馈做了一个简单的LDO,想要应用在1G的VCO上。LDO开环GBW几十M增益100dB,闭环特性如下:Phase Margin=83.7(Deg) @ freq = 5.4MHzGain Margin=27.7(dB) @ freq=135MHz

仿真的时候,我在LDO输出端加了1uF的电容,还串了一个电阻

但是psr曲线感觉挺奇怪的,高频时候直接到0了,看论文上一般不会到零,高频时还会有所提升,想请教下我的问题出在哪里;

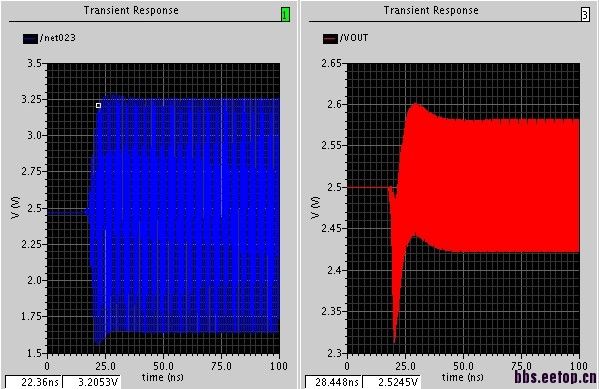

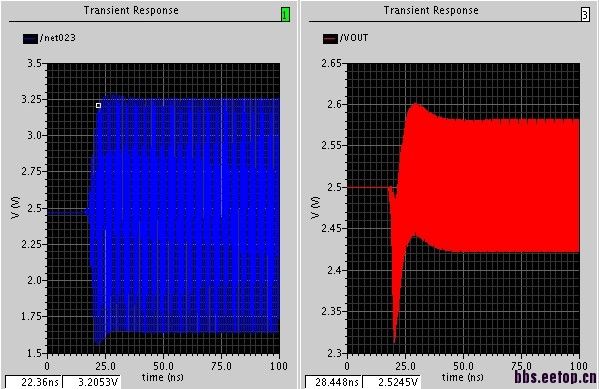

另外,我把LDO和VCO接在一起发现会有轻微的震荡,但却没有影响VCO功能和相噪,也想请教一下大家这个问题,非常感谢!

]

]

仿真的时候,我在LDO输出端加了1uF的电容,还串了一个电阻

但是psr曲线感觉挺奇怪的,高频时候直接到0了,看论文上一般不会到零,高频时还会有所提升,想请教下我的问题出在哪里;

另外,我把LDO和VCO接在一起发现会有轻微的震荡,但却没有影响VCO功能和相噪,也想请教一下大家这个问题,非常感谢!

]

]

‘LDO开环GBW几十M’和‘闭环特性如下:Phase Margin=83.7(Deg) @ freq = 5.4MHz’这是什么意思?

esr电阻加的是不是太大了?

如果是内部补偿,PSRR是有可能到0的。Rincon Mora的书上有写

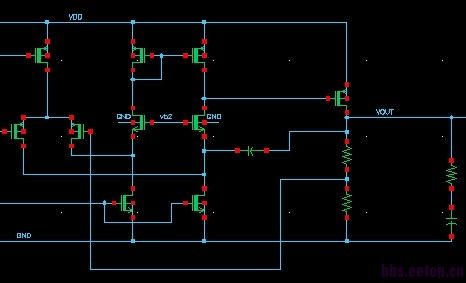

贴电路图吧,说不清楚的

我开环的时候就当做两级放大器仿得,电阻好像是挺大的,看有的资料上写20-200毫欧,我以为只要结果稳定性看着好就可以了,最后电阻有600欧,想请教下这个电阻大小会影响什么呀?

恩 你好 电路就是这样的 一级放大器 加一个功率级 麻烦帮我找下问题吧~

电路图我贴了 你可以看下 好像也没有什么特别的技术 我如果想应用到VCO上的话是不是需要在高频的时候也有比较好的抑制性能?

大哥。600欧的esr。 你高频时电源上的扰动都完全由这600欧承受了,PSR当然差了

600欧的ESR电阻太大了,高频时PSR受ESR电阻影响很大,瞬态响应的纹波也会大

这个LDO输出振荡了吧

电路用了miller补偿,这个一般是用来把主极点放在功率管栅极,

在外面又加上了1uF的负载,大大降低了输出节点极点频率,这样很难保证LDO环路稳定吧

我觉得加上1uF负载后的Phase Margin应该不会太好

好的谢谢哈!我再看下~

额 原来是这样~不太懂瞎调的 负载电容一般多大比较合适呢?

学习了

你电源是怎么加的?

你可以试试,这种结构的负载电容越大越容易稳定。

能解釋下為什麼嗎?

大概是因为主极点已经是输出极点了