BGR带隙电路中遇到的问题

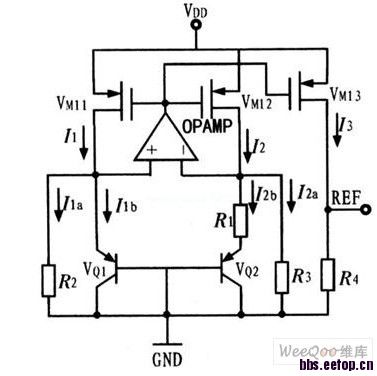

最近我在做一个低压带隙电路,使用的

这种结构,在tt模式下,ppm的值可以到3左右,但是在ss和ff模式下ppm的值就达到了20多,tt的波形的形状是凹的,想问下是不是因为运放的原因导致不同corner下差距那么大,另外这种电路要怎么提高PSRR的值,用的工艺库是0.13um的....补充下运放用简单的二级运放,增益75db,低频电源抑制比有95db

这种结构,在tt模式下,ppm的值可以到3左右,但是在ss和ff模式下ppm的值就达到了20多,tt的波形的形状是凹的,想问下是不是因为运放的原因导致不同corner下差距那么大,另外这种电路要怎么提高PSRR的值,用的工艺库是0.13um的....补充下运放用简单的二级运放,增益75db,低频电源抑制比有95db

没有曲率调整可以达到3ppm?

有点不可思议

这个运放的输入端是不是接反了?

输入端没有接反,我问了老工程师,他说让我把运放改成一级的运放,但是我不懂的为什么要这样改

自己想想咯, bandgap的电流镜带下面的bjt+res也是一级放大器,再加上你的2级opamp

你又不考虑3级放大器的补偿,有可能不稳定

运放输入端极性接反了,自己判断一下,不能老是相信工程师的,PTAT自偏置结构一路为低阻,一路为高阻,运放+端为负反馈,当然要接高阻端了,否则环路不稳定,不信你自己仿一下.提高PSRR可以在IEEE上搜一下相关文章,可以在运放输出端对Vdd接一小电容或增加一路PSSR提高结构(就是运放输出端接一diode),低频PSRR再高也没多大意义,最好10KHz能达到70dB吧,才能应用到LDO或DCDC里

加preregulator

是前仿吧?

呵呵 运放应该是接反了

呵呵 Corner的差距包括BJT的corner了吗?

nice。

preregulator+cascode可以轻松上100dB at 100K,甚至1M

PSRR可以根据实际电路所要求的在系统的工作频率出有多大干扰幅度,以及要衰减到什么程度定;实在不行的话要把BG电路的电源改为LDO 输出,

bucuo。

VM13的沟道调制效应是个问题,相信温度特性好不到那里去

不加preregulator的话,不解决VM13的沟道调制效应,PSRR最高也有个限度。看你要做多低的电压,是否低到连preregulator或者共源共

栅也加不上去。

运放是没有接反的 自己画一下负反馈环路就知道了

可以做一个功耗10uA以下的preregulator,效果很不错,能psrr增加40~60dB

当时看了你的回复,有些不明白,刚又翻了一下书,对于自偏置电流镜来说,OP输出端对于电流的贡献是负的,这里就相当于是负反馈了,而一路高阻,一路低阻,OP正负极输入相当于电流流过两路阻值得到的电压,而负反馈必须要大于正反馈,所以OP正极一定要接高阻。而对于拉扎维P316图11.11的电路则是由OP输出端提供电流,OP输出端对于电流的贡献是正的,恰与自偏置的情况相反,所以OP正极要接低阻了,所以觉得不能一概而论说BGR OP的正极一定要接高阻,还是要看一下反馈极性。

运放建议可以采用折叠运放,稳定性比较容易调整!PSRR就按照大家说的即可!

先调整好AC特性,再调TC吧!

这种结果,温度曲线应该还是开口向下的,TC主要受电阻的温度系数和PNP的温度系数影响比较大,尤其是PNP!

应该是接反了吧

把极性改过来,再仿仿看是什么情况。

请问基准输出端是接一个连接到VDD的电容可以提高PSRR吗? 那接一个连接到地的电容呢?

如果没想错,基准输出端连接一个够大的电容到VDD,应该可以把所有VDD变化的绝大部分都耦合到基准电压,得到~0dB的PSRR。

肯定是运放输入极性接反了!

看了你的回复 觉得思路更加清晰

学习中啊 ,加油

极性应该是反了

可以提高高频的PSRR

挺牛的啊。我仿真了一下我们已经作成产品的带隙基准回路,在Typ下的ppm最大值48呢(-30到-20的时候)

大侠,你怎么看

ppm咋计算的呀

比如说我跑了个仿真(基准:1.21V)(温度:-30~95)这两点的电压差为X(mV)那么温漂这样计算对吗?

X*1000/(125*1.21)