LDO的零极点跟踪补偿问题

另外我还在第二级后面加过一个buffer(跟随器),然后降Cc接到第二级运放的输出段,还是看不到零点。

顶一下,帮帮忙吧

icrease Mc channel length(ex 5u,10u or 20u) and check AC analysis

这个补偿方法,似乎根本不可行。以前推导过一次,会增加一个零点,但与此同时又引入了一个差不多的极点。

好像以前试过不行哈

这个管子的尺寸我改过很多种,并每次检查这个管子的等效电阻,但是就是无法产生零点。

而这个补偿方法好多篇论文里面都用了,半导体学报上就有两篇用了这个结构(是运放后面又加了一个buffer),按道理来说这个原理应该不会有问题啊,实在很郁闷。

mc的静态工作点是什么?没有下拉网络?

这样子的结构,就像dengqin所说的,产生了一个零点,却同时产生了一个极点,而且这个极点的频率也是比较低的。我建议你把A2设计成一个buffer, 把Power PMOS gate 上的极点推到高频。然后把Cc接到P1那个点,这样子的寄生极点就小很多。

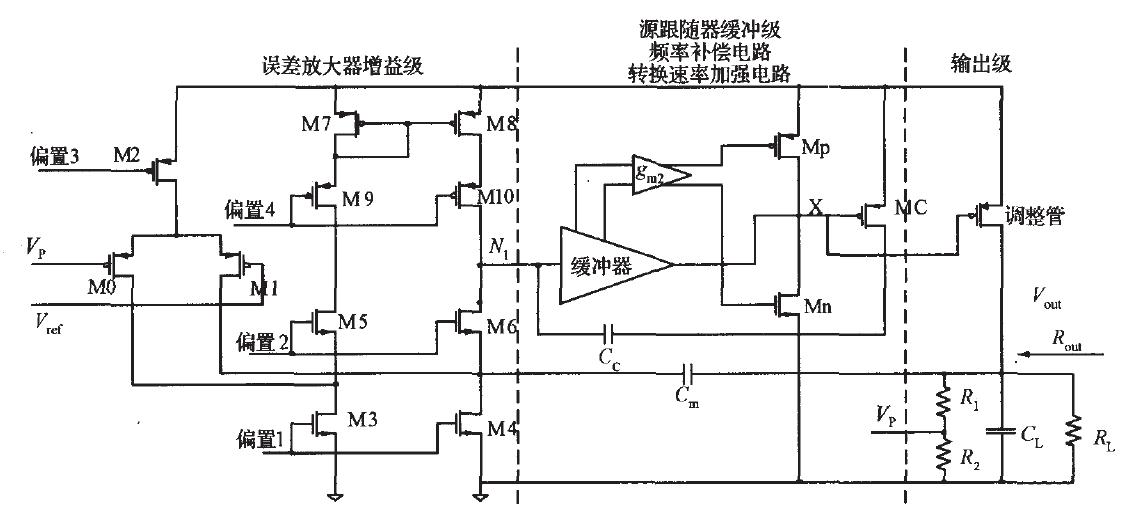

hdqwr你说的结构应该和下面这个图差不多吧,但是我在仿真的时候,这个零点还是看不到,真是奇怪。

你仿真这个结构吗?零点能出来吗?

尽信书不如无书

9# gm-cfiltersz

这种接法,一样啊。同样会产生一个极点。这种方法,我觉得基本上就是不可行的。推导过一次,发现产生的极点,比零点更低。接到第一级的输出级,同样会产生零点和极点的啊。

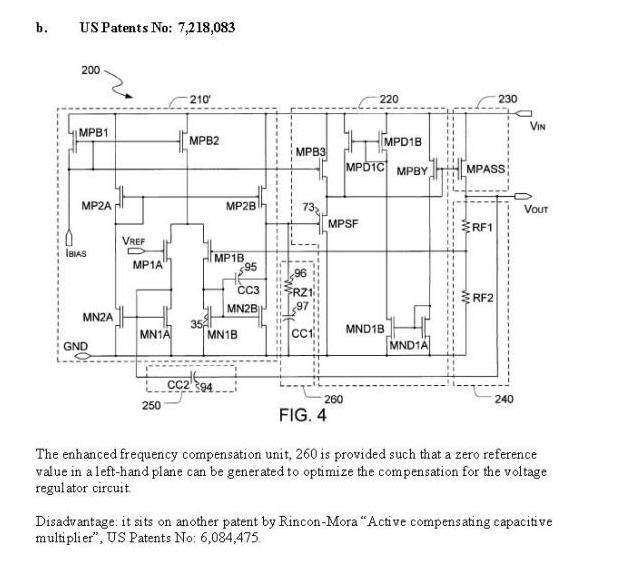

This one may be able to help you.

In your circuit, if I am not wrong, please correct me.

Cm is the compensation cap (dominant pole)

Cc and MC is left-hand plane zero to optimize the compensation.

yeoks99:你的理解是对的,在多篇论文中都提到了这样的结构。但是我在利用这样的结构进行仿真的时候这个左半平面的零点根本不出现,明天我去把传输函数推导一遍,看看到底怎么回事。

我换了工艺仿真了一下,回复9中的做法没有问题。但是在我现在用的这个工艺中就是无法实现,比较气愤啊。

但是这个方法感觉意义不大,产生零点同时也产生了极点,极点比零点低一些,dengqin 同学的说法很有道理。

It will be useful if you are using miller compensation technique not active capacitve current muiltplier in some design.

设计的时选用结构要和工艺结合

该方法理论上很完美,但实际的结果并不好

interesting

LDO有个很好用的方案,TI也在用,这个文章发表在2007年的ISSCC上,曾经做多个LDO的review和实现,个人以为那个方案是当前工艺下最接近完美的了。方法大概是将一个极点通过反馈将其推到工作区之外,将工作区内的极点数减少从而使整个工作区内完全稳定,裕度100度左右,当然那个文章里提到的可以再改进下

dddddddddddddddddddd

请问下那篇文章的题目是什么?我想下载来看看

看不懂啊……

没用过这个补偿结构

好久没玩LDO了,跟踪学习下

同求paper。

真想看看是哪片?

把补偿的 mCRC 通通放到第一级运放的后面 第二级的运放做成buffer,输出电阻做小,使得由Rbuffer*C大管 构成的极点在单位增益带宽之外这样整个系统就剩下 运放第一级极点 补偿的零点和R大管*Cout构成的极点了 是可以稳定的

这个结构和用补偿电阻的结构相比有个问题,就是相位裕度随输入电压变化,仿真需要仔细检查各个输入电压和corner、温度下的频率特性。

求paper