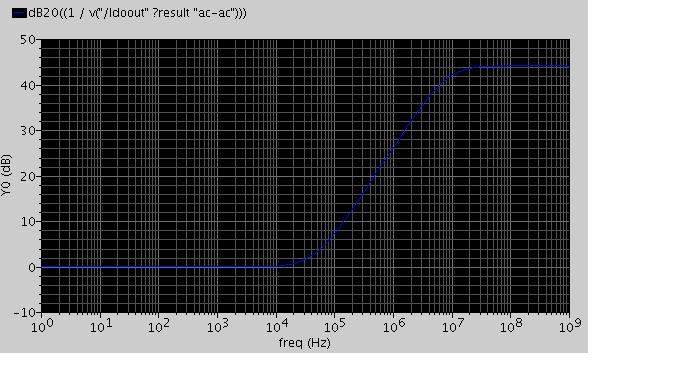

如何提高LDO的低频PSRR? 附图 分析

特别是10M以下很差,如何改进设计呢?

谢谢大家指点

看你图不对吧,PSSR理论上是低频好,高频差,是不是仿错了?

问题

你的这个好像是有问题的

ur simulation must be wrong

确实是反了。 但是

运放里面的定义是PSRR=Av/Add其中Av=Vo/Vin ; Add=Vo/Vdd

但是LDO里面不知如何定义 Av=Vo/Vin?

是不是PSRR=1/Add或者分贝 20log(1/Add)?

下面的仿真图对了么?

通常DC部分的PSRR是负值

仿真方法可以参考allen的书第6章

低频端的PSRR主要取决于你的ERROR AMPLIFIER的PSRR,你把它做好就行了

谢谢

现在主要的因素还是LDO的低频段PSRR上不来,1MHZ以上的有40DB的PSRR,应该还不错的。

但是1MHZ一下的就很差了。

谢谢提示关注误差放大器,只是不知道如何去克服?

输出和电源之间加电容试试

low frequency psrr is better than high freq. Something is wrong.

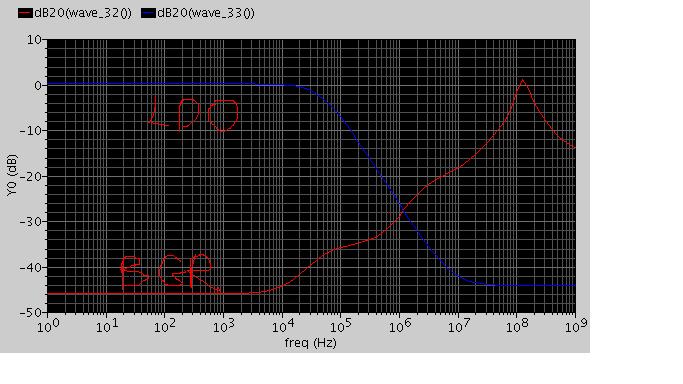

带隙基准的确是低频PSRR要好些。

但是LDO的输出有大电容,高频PSRR是有保证的啊。

现在即使将LDO的带隙基准源用理想电压源取代,对LDO的仿真还是会发现低频段很差,高频PSRR很好(有输出大电容)

LDO系统的PSRR仿真和LDO内部的带隙部分的PSRR如图

可以发现低频部分的LDO PSRR很差。

小编,你是不是自学模拟电路?

自学,难道还有什么其他方式?

当然还有请教你们啊。

试过了 没有用啊

肯定是哪里出错了

看看你的工作点(包括电压和电流)正常吗。

ac分析工作点有问题吧

应该是弄错了

模拟的图还是不对呀,应该从负多少dB开始往上升

比较奇怪,倒像是仿真了地上的psrr

PSRR 在低频段不会有问题的

在LDO里比较特殊,有一个PSR的定义,直接算输出对电源信号的抑制

ldo里的psrr不是我们通常意义上讲的power supply rejection ratio,而是power supply ripple rejection,就是前面有人说的psr的意思,不用去求比值

不明白楼上说的是什么意思。求详解。

的确有问题 仿真有可能出问题了吧

加个可变电容——MOS电容来稳定电源电压的纹波

你这个是PSR?

cvffddgg

电源加ac 源ac仿真 plot输出低频的psrr是由直流增益决定的

这不符合常理,一般情况下高频psr比较差

LDO的仿真是针对PSR吧,运放的才有PSRR。lz的定义好像没有搞清楚吧。