关于一个二级运放的若干细节问题

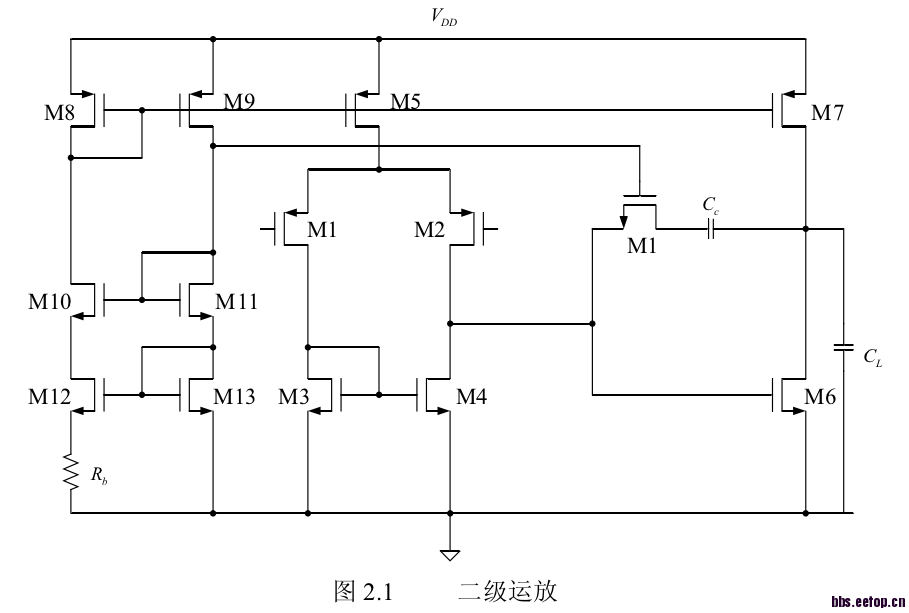

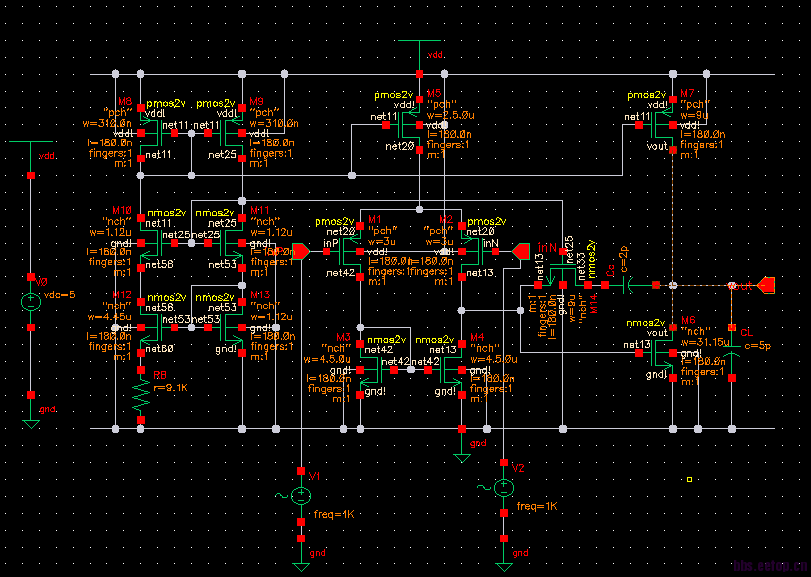

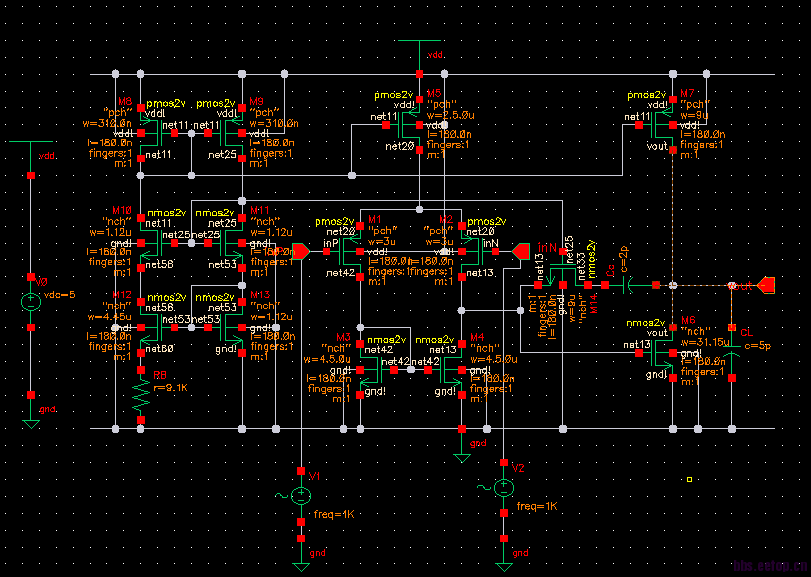

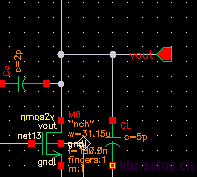

问题二:下边是本人借用网上的一个二级运放,对于具体工作细节不是很了解,忘予以解答。

1、为什么采用镜像源做驱动,或者说电路图中的驱动电路和下面这幅驱动相比有什么优点?

1、为什么采用镜像源做驱动,或者说电路图中的驱动电路和下面这幅驱动相比有什么优点?2、对于图2.1而言,因为驱动电路中的两条支路电流相同,如果M8=M9,M10=M11=M13(均指长宽比,或者管子参数完全相同),如此要形成对称结构(是不是全部驱动就是电流镜结构,或者是只有一部分是电流镜),则要要求M12和电阻Rb的和=M13的电阻。为什么别人计算的是Rb=1/gm13,难道不考虑M12的影响?还是因为采用了那个4倍关系造成的误差。

3、这里电阻的作用是什么?为什么不直接让M12=M13,如此对称性不是更好?

4、外加信号加在了两个NMOS的栅极上,当然是通不过去的,只是控制两个MOS沟道导通后的电流的,往往输入信号很微弱,那么能保证MOS导通,是不是就是要计算的的长宽比之类的决定的?有的资料上说,差分级的MOS也得工作在饱和区,但是不是说,达到饱和后,多余的电压大都加在耗尽区上,不再贡献源漏电流了吗?如此,当要放大的信号超过,哦,犯糊涂了,那是源漏电压,不是栅极电压。这个不算

5、第一级的输出对第二级的M6起偏置作用,对那个补偿电容起充放电作用吧?中间的差分电路是对称的,对吧?看那个差分输出节点,电流分流方向向上和向右,由于那个多余的触角作用,会不会影响差分的对称性?(因为别人做的说M1=M2,M3=M4。)我想,电路上加了输出后,对差分绝对是有影响的呢。

如此就又引出了一个问题,即到底对Cs充放电的电流是差分的右边输出提供的呢,还是整个差分提供的呢?因为从电路上来看,如果将输出移动到M5的下边,好像才是总的差分的功效。但是就这个图2.1,好多人的论文中计算那个转换速率SR(转换的是什么呢)用的是晶体管M5的饱和电流/Cc,结果他们算出来是60,但是实际上只有35左右。我觉得是用0.5倍的M5的饱和电流去算更合适,毕竟这里对Cc充放电的应该是差分右边的那条支路吧?这里忽略掉那个多余的触角的影响,所以应该是30(触角的影响算是5).如果这一点我错了,还望大侠们能予以指正。

问题有点多,希望大家不要嫌麻烦呀。

另外再问一个问题:.18um工艺,指的是所用的晶体管的沟道长度是0.18u吗? .18工艺中能让晶体管的沟道长度为1um吗?1微米的话是不是就算是1um工艺了?还是说这只是一个工艺,只有下限没有上限。即,0.18um工艺中也可以使沟道长度等于1um呢?

我设计的管子沟道长度统一是1um的,但是我们ASIC上学习的都是0.18微米的。能不能把所有管子的长宽比不变,把长度都改成0.18微米呢?这样子对电路性能指标会产生影响吗?

还是先把电路适当分解好再分析更有效率一些

1、采用电流镜更精确

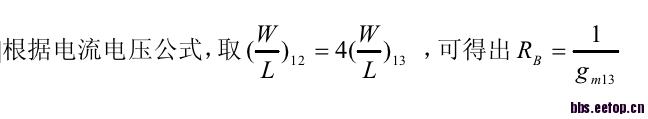

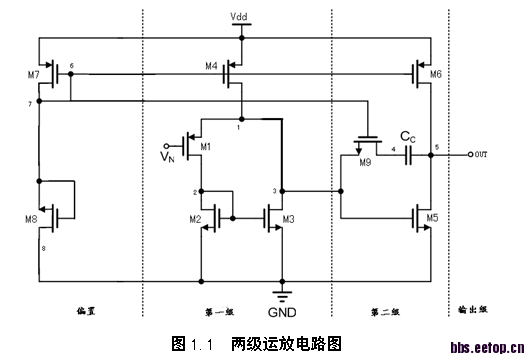

2、由于W/L12=4(W/L13),所以,Vgs12-Vt=0.5*(Vgs13-Vt),故而可得到电阻R的值为1/gm13

3、这是个自偏置电压源。如果像你说的,去掉电阻,采用M12=M13,那存在许多简并点,电路无法启动。只有像这样,线性源和非线性源互相作用,电路只存在非0外的一个简并点

5、SR是大信号特性,而你是按照小信号来分析的,会得到错误的结论

0.18um工艺指的是这个工艺所允许的最小栅长是0.18um,大于这个值得栅长都是被允许的。采用最小栅长,速度会变快,但是本征增益会下降

只要肯下功夫,转行当然是可以的。但做模拟非常累,何况你是转行的,LZ慎重。

嗯,谢谢你。累倒是不怕,我喜欢电路,特别的想把其中每个元件的作用都弄清楚,觉得电路很有意思,现在我每天都呆在实验室看电路,觉得很有意思,也很喜欢这种充实的感觉。

对于你说的那几种答案,我都没有听说过。

(比如电路简并点,是不是零点和极点呀?简并是不是指的是:分子上或分母下,等于零的因子是高次幂呢?简并造成的影响是不是电路震荡呢?零点是不是系统导致输出为零的点呢?还是说零极点的定义只是从传递函数的形式上来定义的?总觉得应该是有物理实质的。其在电路上的定义总不能说:零点就是振幅和相位开始单调递增的转折点,极点就是单调递减的点吧?我觉得要是象"零点就是导致系统输出为零的点"这样子简明扼要的定义就好了)

不过前辈说得话听起来很有道理的。下去我会好好弄懂那几个概念的,再次谢谢你。

上面提到的简并点应该是指电路的两个稳定直流工作点。

是指上下都是电流镜的电路,存在两个稳定的情况。

一种是两个电流镜支路流过的电流都是零

一种是两个电流镜支路正常流过电流的情况

这种所说的简并的电路,一般是加一个启动电路,让电路启动的时候偏离第一种情况

还有零点是输出为零的点,系统函数上也可以看到,我们做估算的时候也是用这个概念,但是这样的解释应该不能完全概括零点的特性

LZ的数学功底和抽象思维应该不错,学电路应该是没问题的,只是要做好持久战的准备了

我也是本科学物理,现在研究生在学电路的,也是初学,有问题我们可以交流下 QQ:549073987

我建议LZ先看一套国外的模拟电路教程和看一本模电的教材,慢慢来 先学习模电的相关基础知识

嗯刚开始看拉扎维的不过不知道和艾伦的比入门看哪个更好呢? 模电都学过了 当时感觉还不错再复习一遍比较容易的

你的回答让我意识到了 转专业是可行的看! 您的知识都已经这么渊博了 我辈定将您看作转专业的典范加倍努力的相信我学上一阵子对于电路的分析应该不是什么问题了的

谢谢你兄台一起加油

7楼的解释是正确的。我再进一步阐述一下。

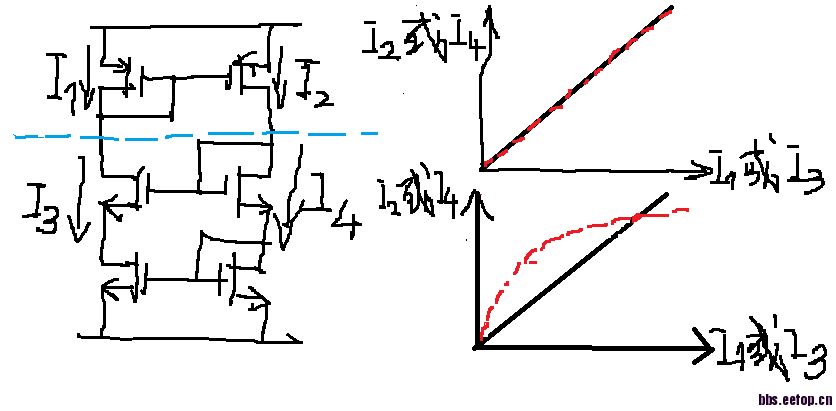

如上图,左边为无电阻的电路。上面和下面的电流镜都是线性源,即I1-I2和I3-I4的关系都是线性的。如右上图所示,当I1-I2和I3-I4两条曲线(黑实为I1-I2,红虚为I3-I4)都是线性的,若两条曲线重合,你就会发现,会有无数个电路可稳定运行的点,若考虑mismatch的话,也会有很多个。这样即使加入启动电路,使电路脱离零值点,那电路稍有波动,就会偏到其他可以运行的点上去,那么整个电路的运行会非常不稳定。这样这个电路是没法工作的。

如果加入电阻,那么下面的电流镜就变成了非线性源。两条曲线只有非0外的一个稳定工作点。这样,加入启动电路使电路脱离零值状态,进入这个工作点,电路就可以一直稳定工作了。

记住,启动电路在电路进入稳定工作状态前一直是正反馈,使电路一直向这个点移动,进入稳定工作点后;启动电路变为负反馈或消除作用,电路就开始工作了。

嗯图要说明的内容是看懂了就是想办法让两条支路电流在电路启动的时候相位不相等

但是难道自始至终都简并的时候(看图,我觉得是指两条支路电流大小适中重合的情况吧),不能起到自偏作用?直接原因肯定是自偏电路也需要启动,否则无法启动电路工作,对吗?但是存在线性源电阻,打破结构对称的时候,上边的电流又是如何通过MOS的呢?比如说管子8、9,毕竟它的栅在刚启动的时候也是没有控制信号的。为什么支路1和2加上线性源不对称了,就可以启动了呢?而对于图1.1单支路偏置的时候就能启动呢?那么对于图2.1的M8和M9,以及图1.1的M7,在电路接通电源的时候,它们是如何自我导通的呢?难道是自激?那么自激的内在因素是什么呢?难道是靠电源开启时的那一瞬的强大脉冲产生的磁感?

难道电流镜稳定性较高的代价就是:严格要求只有当两条支路电流在启动阶段相位不重合才能启动吗?

以上仅是针对自偏电路而言。

再来说一下零极点。

极点:可以说是与电路的每一个节点相关连。每一个节点都有其对应的电阻及对地的电容,这样,每一个节点都可以看成是一个对地的一阶RC低通滤波器,这样就是极点。所以,我们在频率特性曲线中看到的就是在极点后,电路增益的下降,因为电路在到达输出节点前已经有部分信号流向地了。

零点:零点的产生不单单是与一个节点有关,而在于两个节点上信号的相互作用产生的。的确,如你所说,零点就是两个信号在输出节点上的作用相互抵消了,这样就产生了零点

自偏置靠的是线性源和非线性源间的相互负反馈作用工作的。线性源总要求两条支路上的电流是一样的,而非线性源大多数情况两条之路的电流是不一样的,这样,他们就会相互作用,指导这个电路的两条之路上的电流相等,就稳定工作了。自偏置电路往往是要加入启动电路才能进入工作状态的。图1.1是可以不加入启动电路的,但存在一个很大的问题,就是电路对器件的mismatch非常敏感,使得偏置点设置没法精确。而图2.1靠负反馈抑制了电路的mismatch,这样偏置点的设置就精确了

是大小不等,不是相位不等

建议从Paul Grey看起,把razavi和allen放在后面看

建议你把 UC Berkeley的 EE240, 242 以及247 听完学完,你会很有自信,以及很多公司招你的。

顶顶顶,这个可以加精华了

艾伦的那本书要比拉扎维的挖掘深些

学习了。

下边的建议一起感谢了。

那是不是说要想启动还要外加电路呢,这个电路是不能工作的,就是那个电流镜偏置的那个。

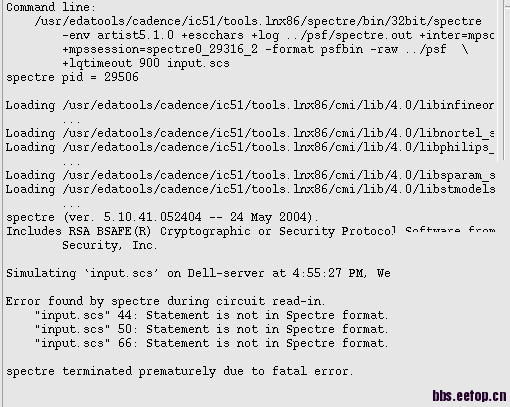

我用保存那个电路的时候出现了以下提示,但是我导师这两天不在学校,网上也实在是找不到答案。能帮我看下原因吗?

这个警告有影响吗?

电路图结构上没有什么问题吧。

ADE环境下跑的时候,提示这个错误。其中两个输入端我把相位一个是0,一个是180了。这个是不是只是说了哪个文件出现错误了,不能得到其他的信息呀。

ADE环境下跑的时候,提示这个错误。其中两个输入端我把相位一个是0,一个是180了。这个是不是只是说了哪个文件出现错误了,不能得到其他的信息呀。图中的参数是我按比例缩小了的,其中那个电阻和电容的大小我没有变,这个应该没有影响吧。暂时不考虑沟道调制。

谢谢

艾伦的要挖掘的更深一些,拉扎维的话夯实基础的,都为“圣书”。

打开input.scs文件看一下

只写后边的吧这么多我等下也看下您也帮扫描一下这种文件我以前从来没有看过的还不知道怎么看它

V1 (inP 0) vsource dc=vcm1 mag=500.0m phase=0 type=sine freq=1K

V2 (inN 0) vsource dc=vcm2 mag=500.0m phase=180 type=sine freq=1K

V0 (vdd! 0) vsource dc=5 type=dc

M12 (net58 net53 net60 0) nch l=180.0n w=4.45u m=1 ad=2.136e-12 \

as=2.136e-12 pd=9.86u ps=9.86u nrd=0.0606742 nrs=0.0606742

M3 (net42 net42 0 0) nch l=180.0n w=4.5.0u m=1 ad=1.2e-11 as=1.2e-11 \

pd=50.96u ps=50.96u nrd=0.0108 nrs=0.0108

M13 (net53 net53 0 0) nch l=180.0n w=1.12u m=1 ad=5.376e-13 as=5.376e-13 \

pd=3.2u ps=3.2u nrd=0.241071 nrs=0.241071

M6 (vout net13 0 0) nch l=180.0n w=31.15u m=1 ad=1.4952e-11 as=1.4952e-11 \

pd=63.26u ps=63.26u nrd=0.00866774 nrs=0.00866774

M4 (net13 net42 0 0) nch l=180.0n w=4.5.0u m=1 ad=1.2e-11 as=1.2e-11 \

pd=50.96u ps=50.96u nrd=0.0108 nrs=0.0108

M14 (net33 net25 net13 0) nch l=180.0n w=9u m=1 ad=4.32e-12 as=4.32e-12 \

pd=18.96u ps=18.96u nrd=0.03 nrs=0.03

M11 (net25 net25 net53 0) nch l=180.0n w=1.12u m=1 ad=5.376e-13 \

as=5.376e-13 pd=3.2u ps=3.2u nrd=0.241071 nrs=0.241071

M10 (net11 net25 net58 0) nch l=180.0n w=1.12u m=1 ad=5.376e-13 \

as=5.376e-13 pd=3.2u ps=3.2u nrd=0.241071 nrs=0.241071

M7 (vout net11 vdd! vdd!) pch l=180.0n w=9u m=1 ad=4.32e-12 as=4.32e-12 \

pd=18.96u ps=18.96u nrd=0.03 nrs=0.03

M1 (net42 inP net20 vdd!) pch l=180.0n w=3u m=1 ad=1.44e-12 as=1.44e-12 \

pd=6.96u ps=6.96u nrd=0.09 nrs=0.09

M2 (net13 inN net20 vdd!) pch l=180.0n w=3u m=1 ad=1.44e-12 as=1.44e-12 \

pd=6.96u ps=6.96u nrd=0.09 nrs=0.09

M8 (net11 net11 vdd! vdd!) pch l=180.0n w=310.0n m=1 ad=2.074e-13 \

as=2.074e-13 pd=1.88u ps=1.88u nrd=1 nrs=1

M5 (net20 net11 vdd! vdd!) pch l=180.0n w=2.5.0u m=1 ad=6.72e-12 \

as=6.72e-12 pd=28.96u ps=28.96u nrd=0.0192857 nrs=0.0192857

M9 (net25 net11 vdd! vdd!) pch l=180.0n w=310.0n m=1 ad=2.074e-13 \

as=2.074e-13 pd=1.88u ps=1.88u nrd=1 nrs=1

RB (net60 0) resistor r=9.1K

Cc (net33 vout) capacitor c=2p

CL (vout 0) capacitor c=5p

simulatorOptions options reltol=1e-3 vabstol=1e-6 iabstol=1e-12 temp=27 \

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \

digits=5 cols=80 pivrel=1e-3 ckptclock=1800 \

sensfile="../psf/sens.output" checklimitdest=psf

tran tran stop=10m write="spectre.ic" writefinal="spectre.fc" \

annotate=status maxiters=5

finalTimeOP info what=oppoint where=rawfile

ac ac start=10 stop=100000000 annotate=status

dcOp dc write="spectre.dc" maxiters=150 maxsteps=10000 annotate=status

dcOpInfo info what=oppoint where=rawfile

dc dc param=vcm1 start=0 stop=5 oppoint=rawfile maxiters=150 \

maxsteps=10000 annotate=status

modelParameter info what=models where=rawfile

element info what=inst where=rawfile

outputParameter info what=output where=rawfile

designParamVals info what=parameters where=rawfile

primitives info what=primitives where=rawfile

subckts info what=subcktswhere=rawfile

saveOptions options save=allpub

是不是从最后这里入手分析呢?这里好像没有说明那个什么细节

解决了

原因是那两个交叉点不能放在一起,我把它们错开就可以了。

但是我不知道cadence为什么这样子规定?

关于你的尺寸问题解释是这样的,0.18um工艺是标准的CMOS工艺,这是一个集成电路的特征尺寸,是一个下限,最小可以做到0.18um。如果你非要设计的是1um的话,不妨选用0.5um的工艺,因为0.18um的工艺太小了,你做的1um比0.18um大 很多啊,会有寄生参数的问题影响你的电路。

还有你提到宽长比不变然后改成0.18um,你想的太简单了,等比例缩小尺寸涉及到很多问题的,电路功能,特别是模拟电路。阈值电压等等吧,很多问题。你还是好好学学基础吧

交叉点cadence规定是又疑问呢,不能确定你的连接关系是否正确需要你二次确认,所以给你个warnning。

啥都不懂,来不及了哈。小伙

拉扎维的书都有讲到。feynmancgz讲得不错。左边是提供基准电流,中间是差分输入,不过M3会存在个镜像极点,会极大影响电路的频响,右边是共源级输出,提供高增益。而中间跨接的电容和M1为密勒补偿。之所以用M1是由于集成电路中电阻不可靠,将M1的栅源电压拉成和M11相同。

做模拟很累?累在哪里?版图?还是什么?难道难度大了就算累?高桥君想知道明白,反正暑假画版图够累了