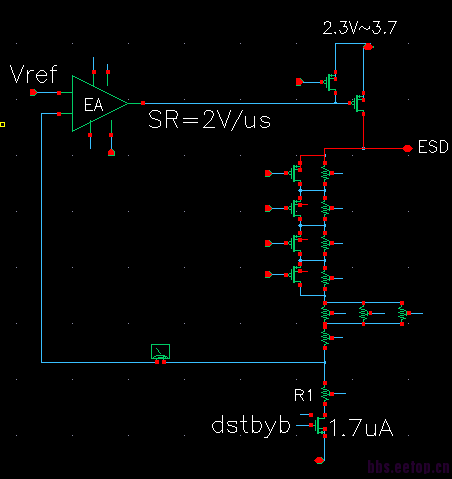

请教一个LDO slew rate的问题

个人感觉,该摆率SR只是上电的时候会有点影响,决定了LDO输出电压从0恢复到正常输出电压所需要的时间。其他的比如负载瞬态特性有影响吗?比如该LDO的负载一直变化时,该SR会有什么影响?还是说负载瞬态特性只由系统环路增益的零极点决定?

另外,环路增益3dB带宽和单位增益带宽跟SR有关系吗?

请高手赐教!

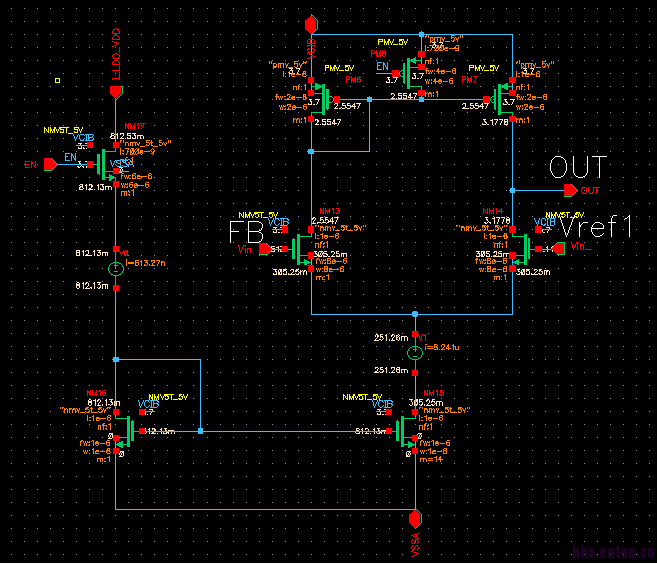

"由于输入电压较低,为了不减小调整管的驱动能力,没有加入buffer,"觉得有点问题啊

“调整管较大,因此寄生电容也比较大”更需要buffer 作为EA和Pass PMOS之间的隔离和电流驱动加buffer会使功率管的vgs损失一个阈值电压,因此减小了驱动,小编是这个意思吧。回小编,负载瞬态特性由系统环路增益的零极点(小信号)和sr(大信号)一起决定的,都和尾电流大小有关系。

是的,就是这个意思(加buffer会使功率管的vgs损失一个阈值电压,因此减小了驱动)。另外,如果负载瞬态变化引起的反馈电压VFB变化不大时,即对运放来说,相当于还是小信号输入的情况下,这是负载瞬态特性是不是就跟SR无关,或者说与尾电流没什么关系?这时的负载瞬态特性完全由环路增益的零极点决定?

哦,可能我没说清楚,是这个意思。加buffer会使功率管的vgs损失一个阈值电压,因此减小了现有尺寸调整管的驱动能力。这样为保证负载驱动能力,需要进一步增加调整管的尺寸。

另外,再请教下,在设计时应该如何考量slew rate的大小呢?有没具体的指标呢?在仿真时,感觉slew rate影响不大。

VFB变化不大时,的确和sr没关系。但怎样使VFB变化不大呢?要么你环路响应非常快,要么你负载波动非常小,当然和输出点电容大小也有关系。小编你可以仿一个负载电流从最小到最大变化的阶跃(上升下降时间100ns)看看。

加buffer会使功率管的vgs损失一个阈值电压,这可不一定,看你加的是什么结构的buffer;对于LDO,error AMP与buffer的结构的选择都需要认真研究。至于ERROR AMP的SR,会对电路的瞬态特性有较大的影响,如果此时你没有较大负载电容的话

如果你的负载有个大的阶跃的话,先是由你的SR决定你的响应时间,然后再由你的GBW决定你的settling时间,GBW跟你的EA的电流当然有关系咯。一般ldo对响应时间都是有严格要求的,所以不是随便定SR和电流的。

EA 一般没有很大的负载能力 如果功率管较大 瞬态响应就不会太好

脉宽多少呢?1、能推荐些buffer结构吗?或者相关资料。谢谢!2、对于LDO,error AMP与buffer的结构的选择都需要认真研究。 。能不能谈谈你的经验

3、如果有外接电容的话,LDO环路的瞬态是不是就不那么重要了。

期待您的回复,谢谢!1GBW跟你的EA的电流当然有关系咯 ,能具体说下关系吗?

有具体的电路吗? 画一个就清楚了.

顶楼有贴电路图

EA的电流会影响第二个极点,也会影响gbw

顶一下