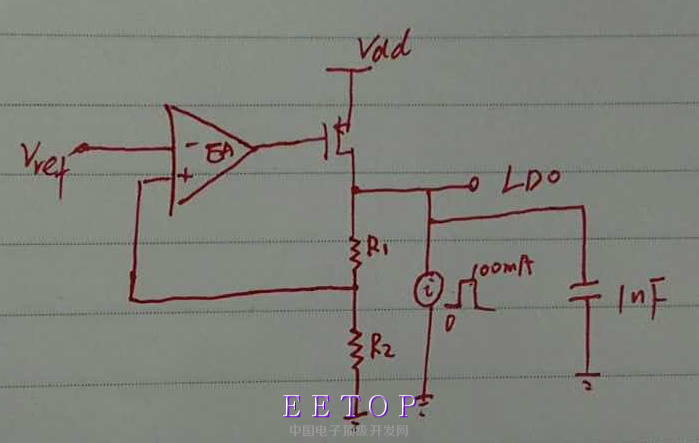

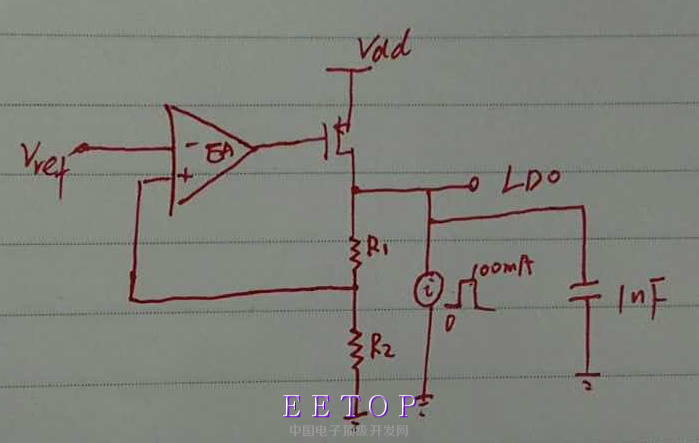

cap-less LDO结构选取

时间:10-02

整理:3721RD

点击:

如题,本屌在研究一种cap-less LDO结构,要求如下:1.CL=1nF

2.负载响应:0~100mA,rise/fall:1uS,ripple<±150mV

3.VDD:2~3.6V,总电流<30uA

各位大佬有没有比较好点的误差放大器结构推荐呀~

我主要的困惑是输出电容比较大,如果结构选取不当,输出很容易成为主极点,这样就不是cap-less的目的了,在一个就是瞬态响应要求比较大,貌似很多瞬态增强电路都木有啥用。

ps:发快啦,这种贴没法悬赏

2.负载响应:0~100mA,rise/fall:1uS,ripple<±150mV

3.VDD:2~3.6V,总电流<30uA

各位大佬有没有比较好点的误差放大器结构推荐呀~

我主要的困惑是输出电容比较大,如果结构选取不当,输出很容易成为主极点,这样就不是cap-less的目的了,在一个就是瞬态响应要求比较大,貌似很多瞬态增强电路都木有啥用。

ps:发快啦,这种贴没法悬赏

一楼自己坐了,顶一下

目前的话,我的output ripple比较大,误差放大器的稳定性还没调好,可能与相位有一定关系,另外是不是和EA的SR也有关系。

跪求瞬态增强电路,或者比较好的 误差放大器

如何降低output ripple呢?求指导,和误差放大器的带宽、相位裕度、SR这些有关吗?

这种指标下的LDO带宽一般是什么量级?

刚接触这个,好多疑问